УДК 681.3.01:51

РЕКОМЕНДАЦИИ ПО ПРИМЕНЕНИЮ МИКРОСХЕМ СЕРИИ К1801

(Окончание цикла. Начало в № 4 - 6, 1988, № 1, 1989)

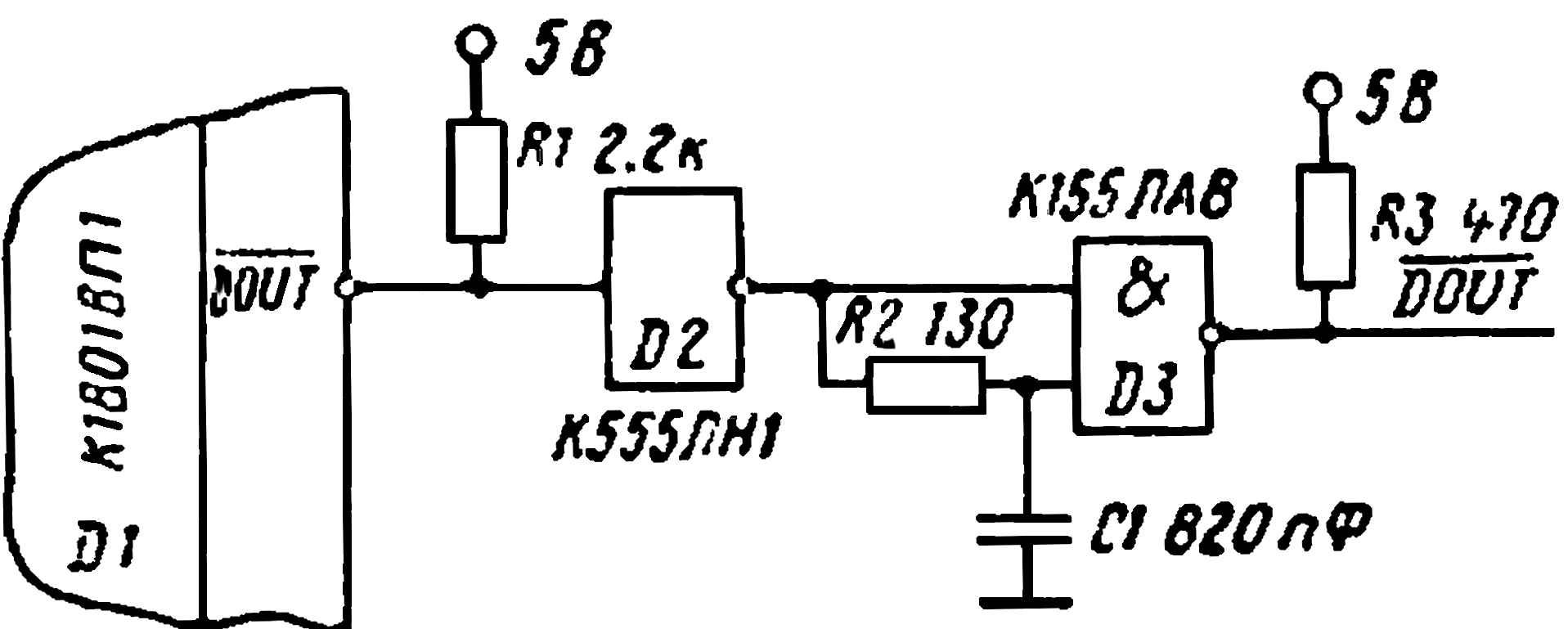

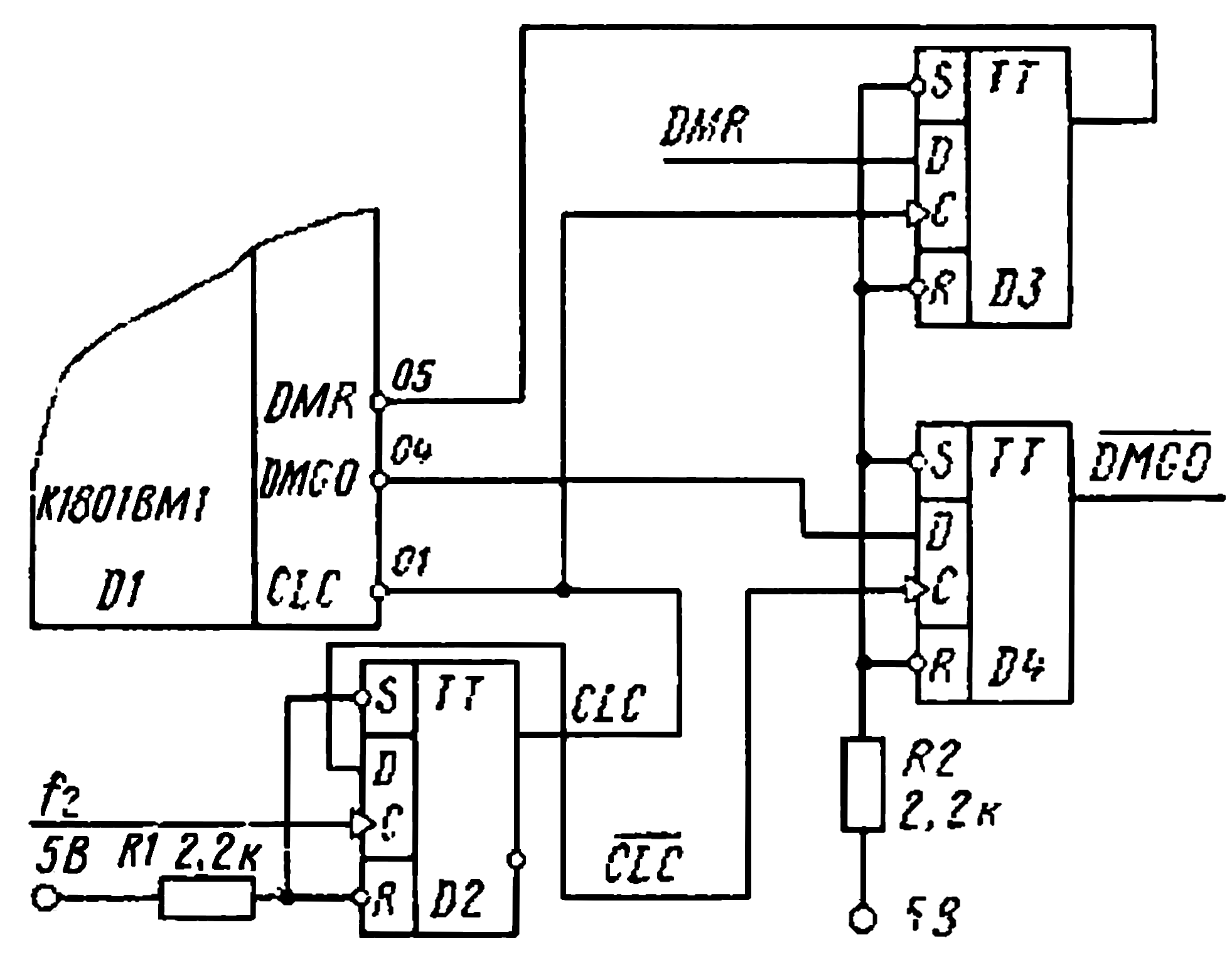

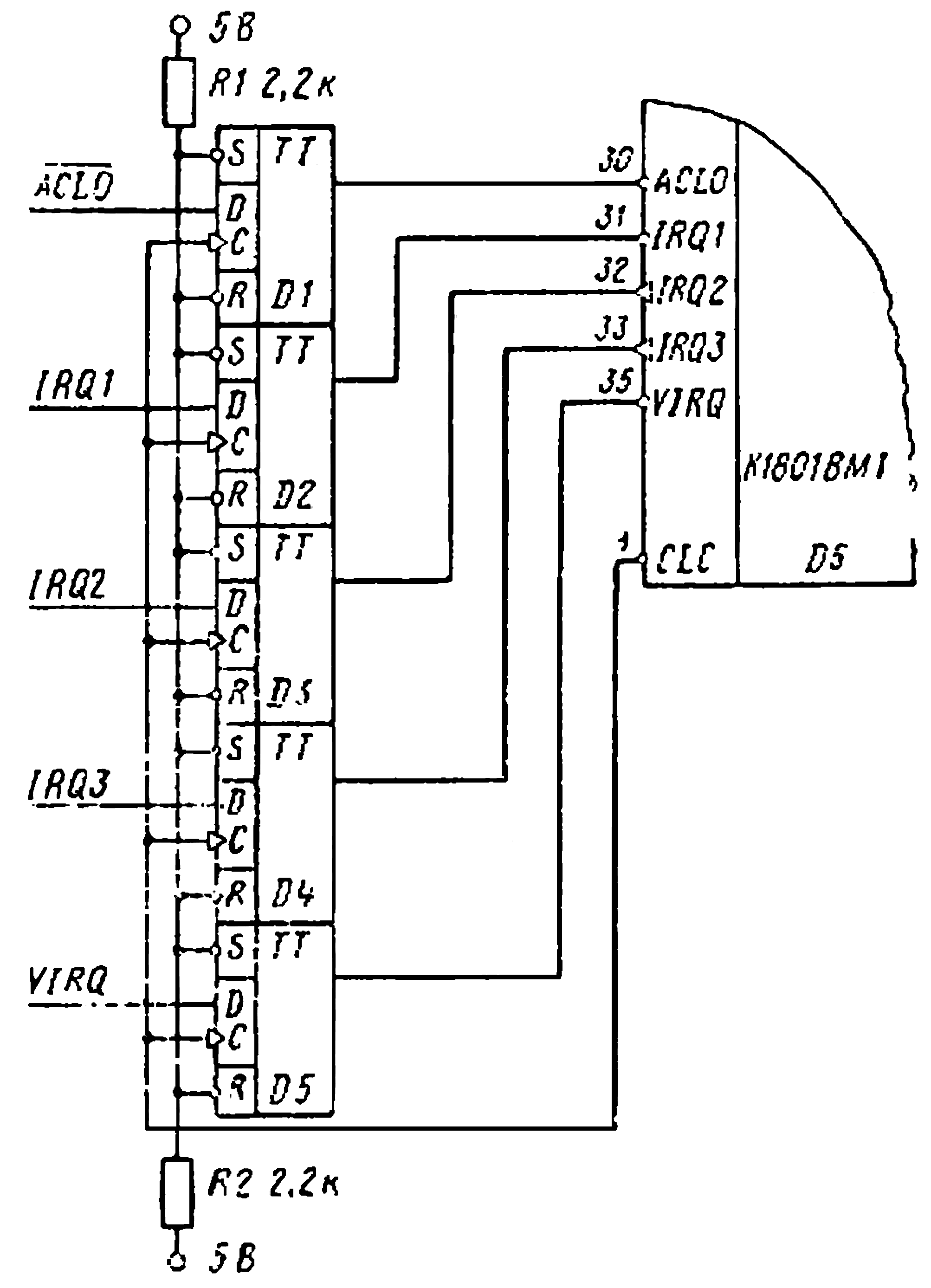

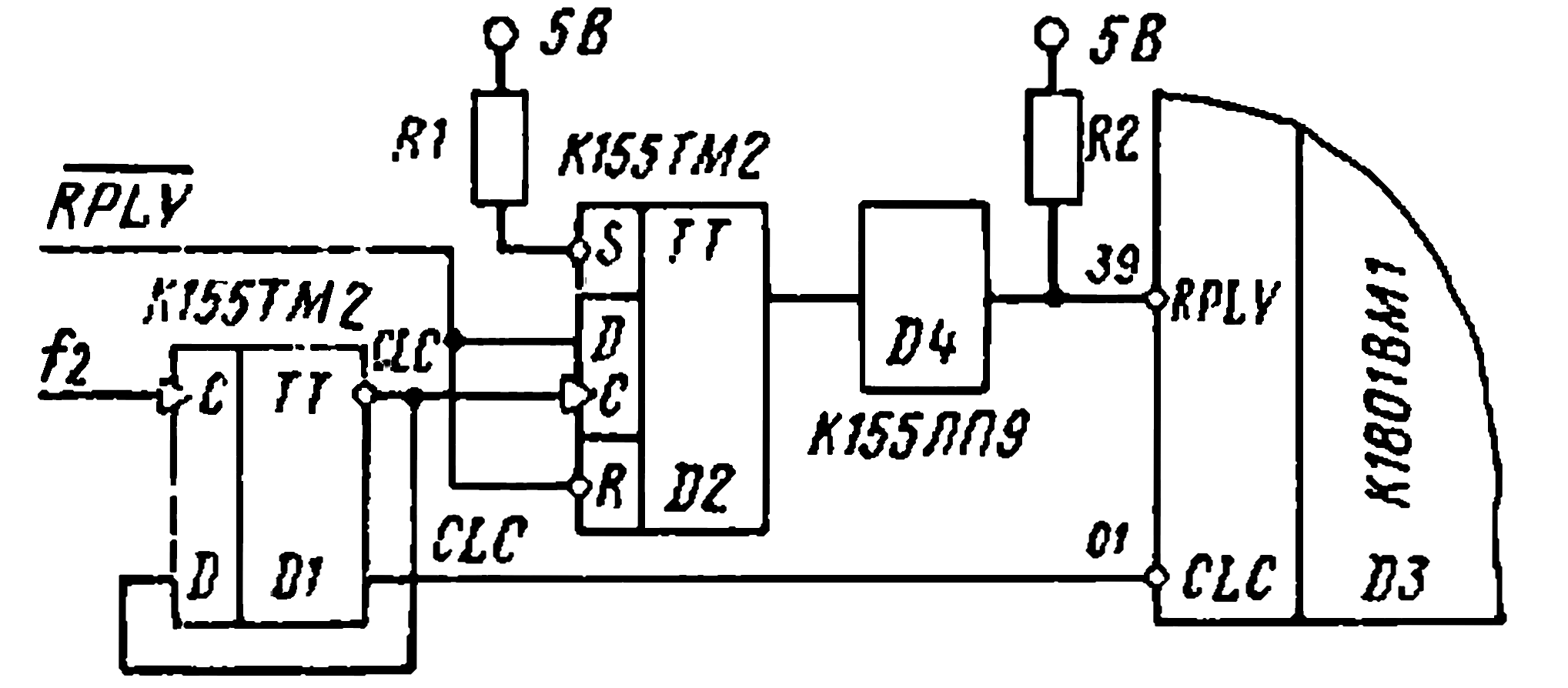

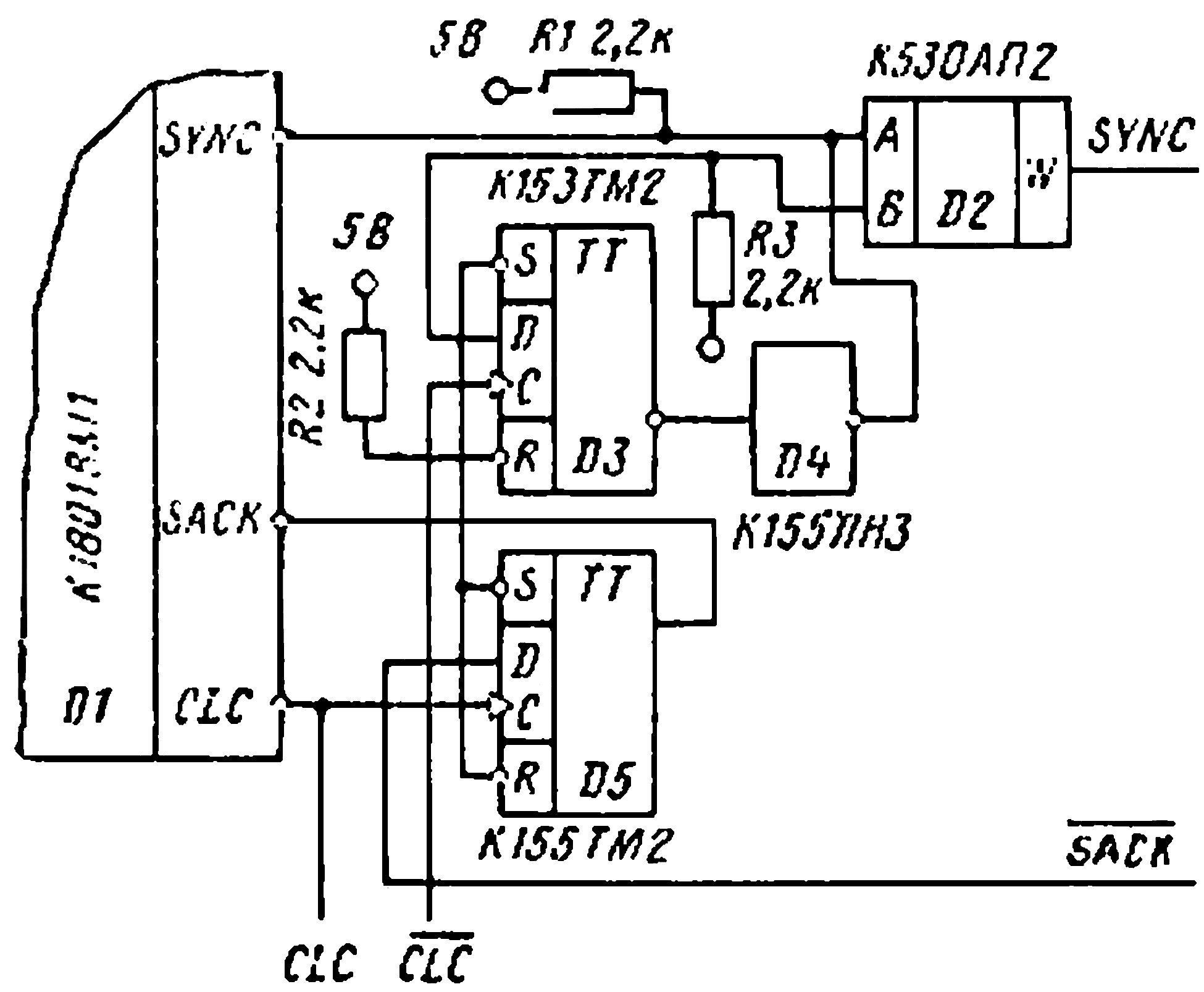

- Аппаратура, сконструированная на основе микропроцессора К1801BМ1, будет гарантирована от сбоев в работе, если использовать «схемы поддержки», выполненные с применением микросхем серий К155, К555, К530 (рис. 1 - 5). Резервные выводы микропроцессора через резисторы 2...3 кОм подключаются к источнику напряжения питания 5 В.

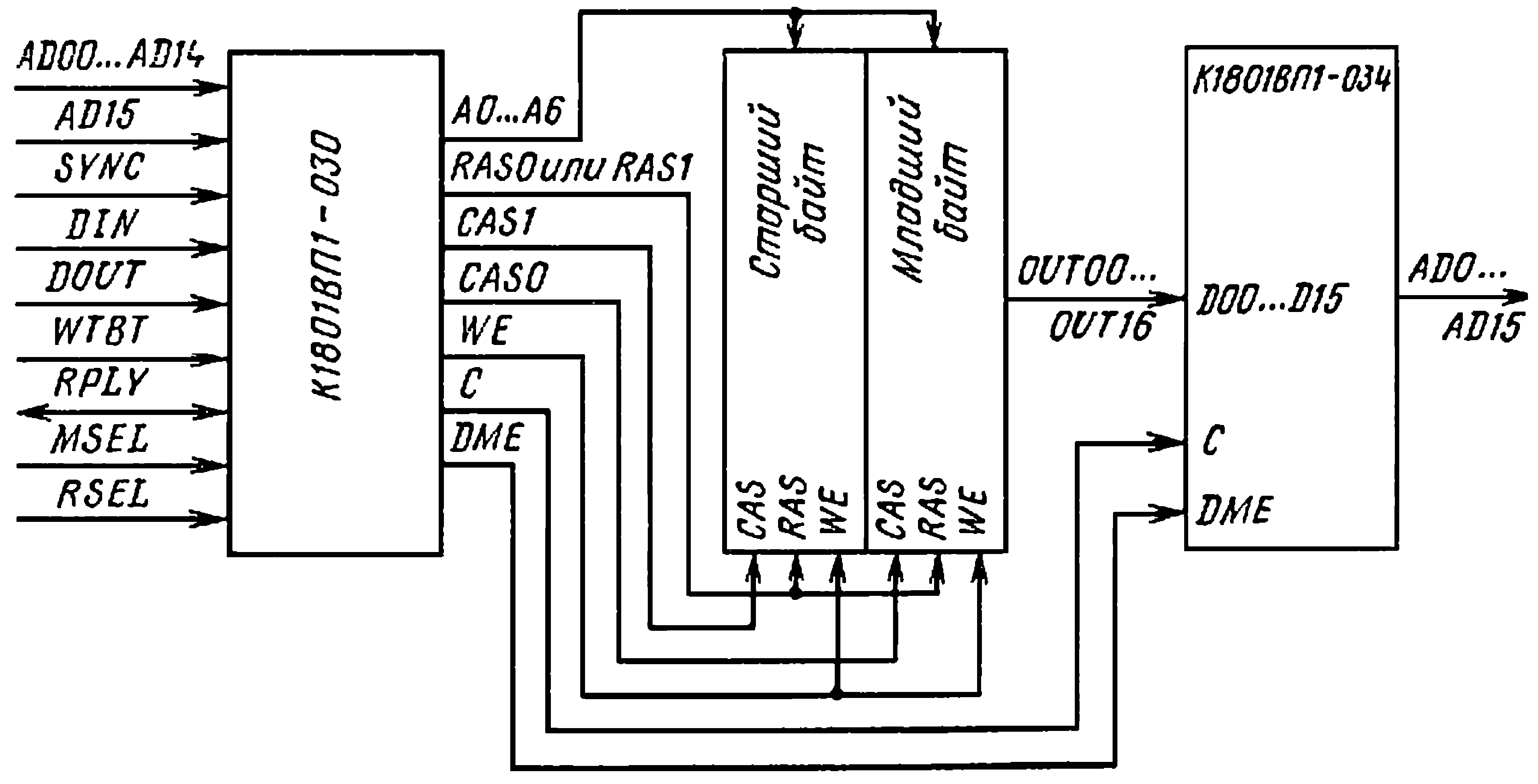

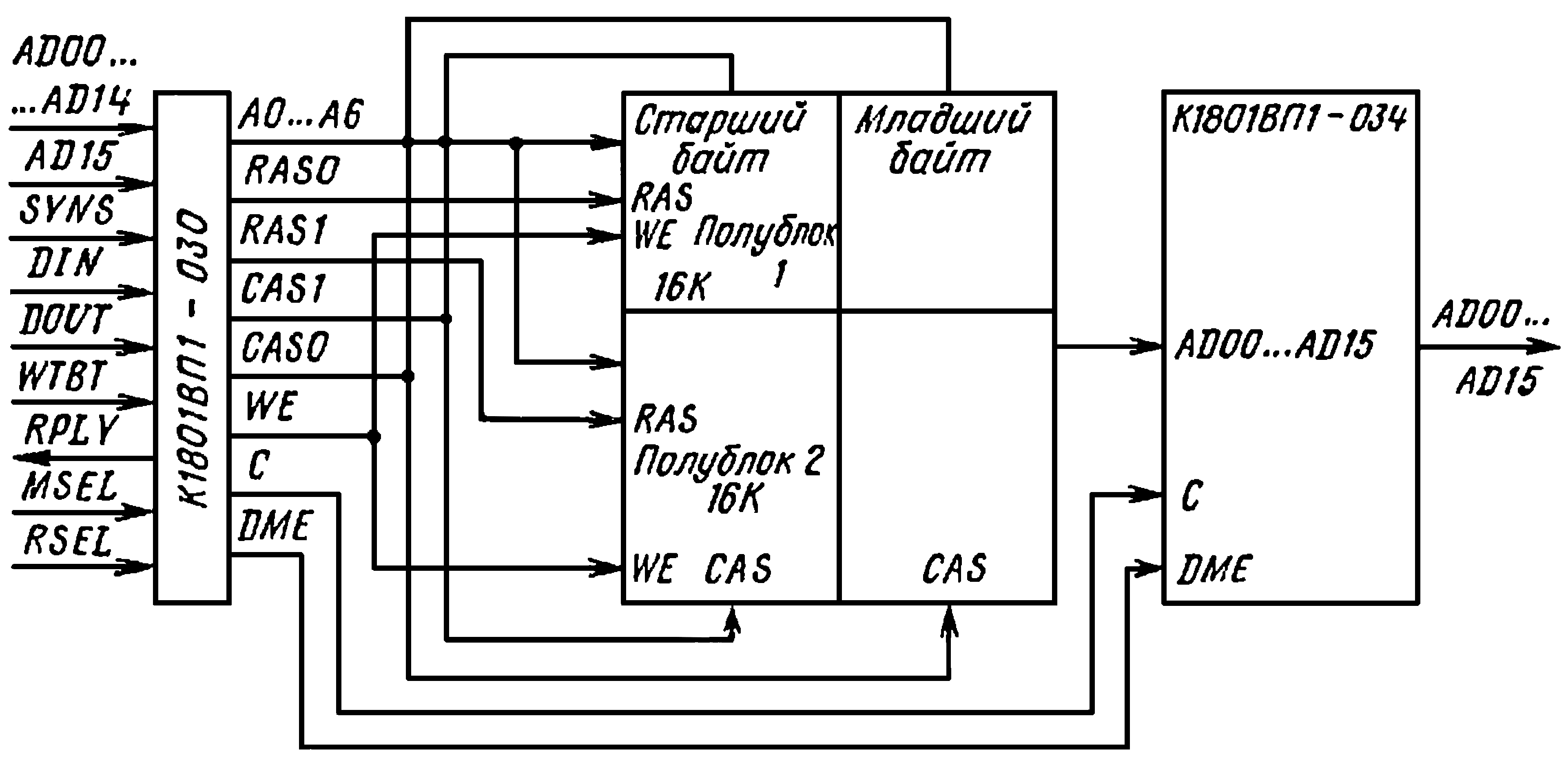

- Примеры применения микросхемы К1801ВП1-030 для управления блоками памяти 16К × 16 и 32К × 16 иллюстрируются на рис. 6 и 7 соответственно.

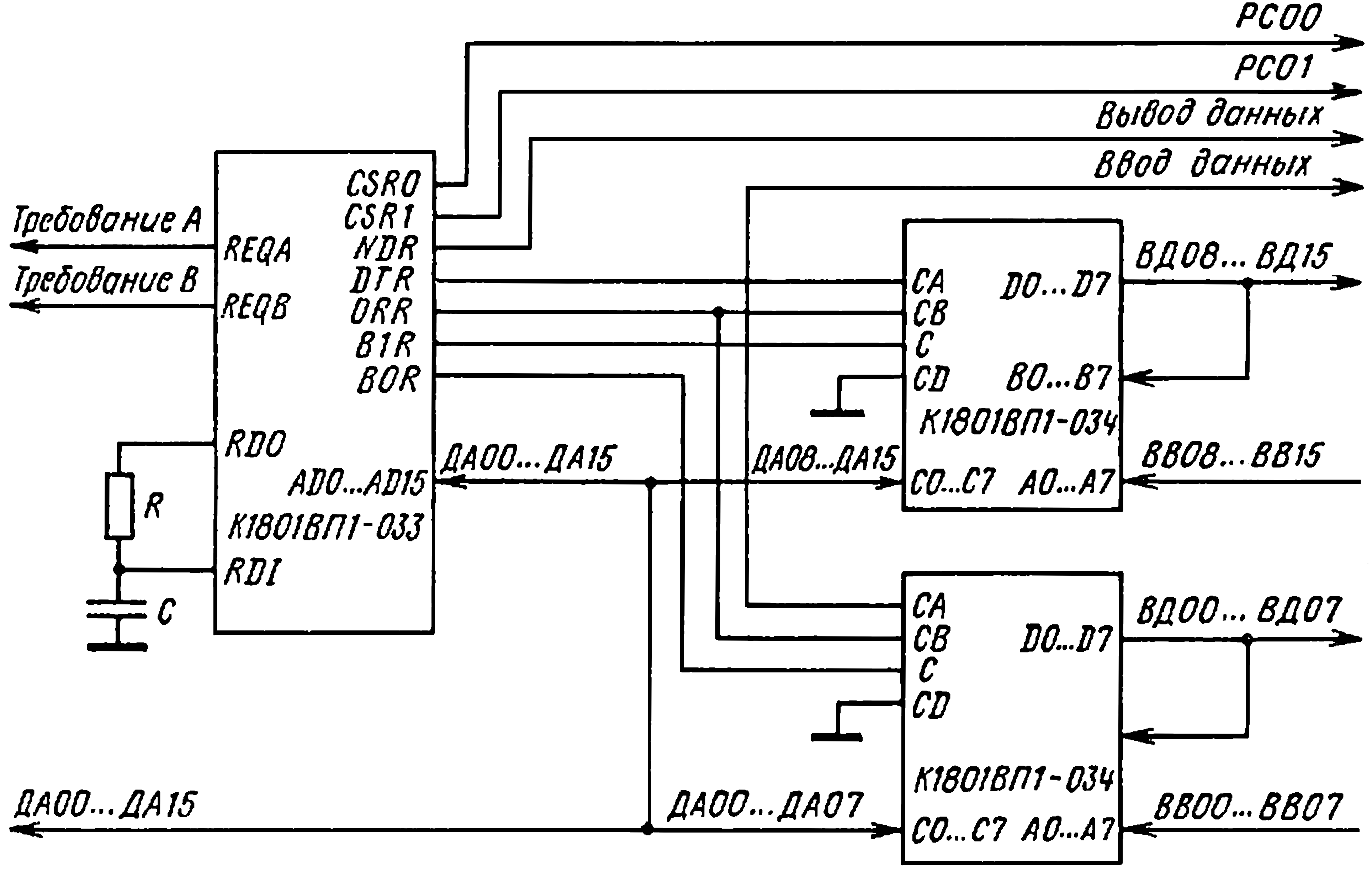

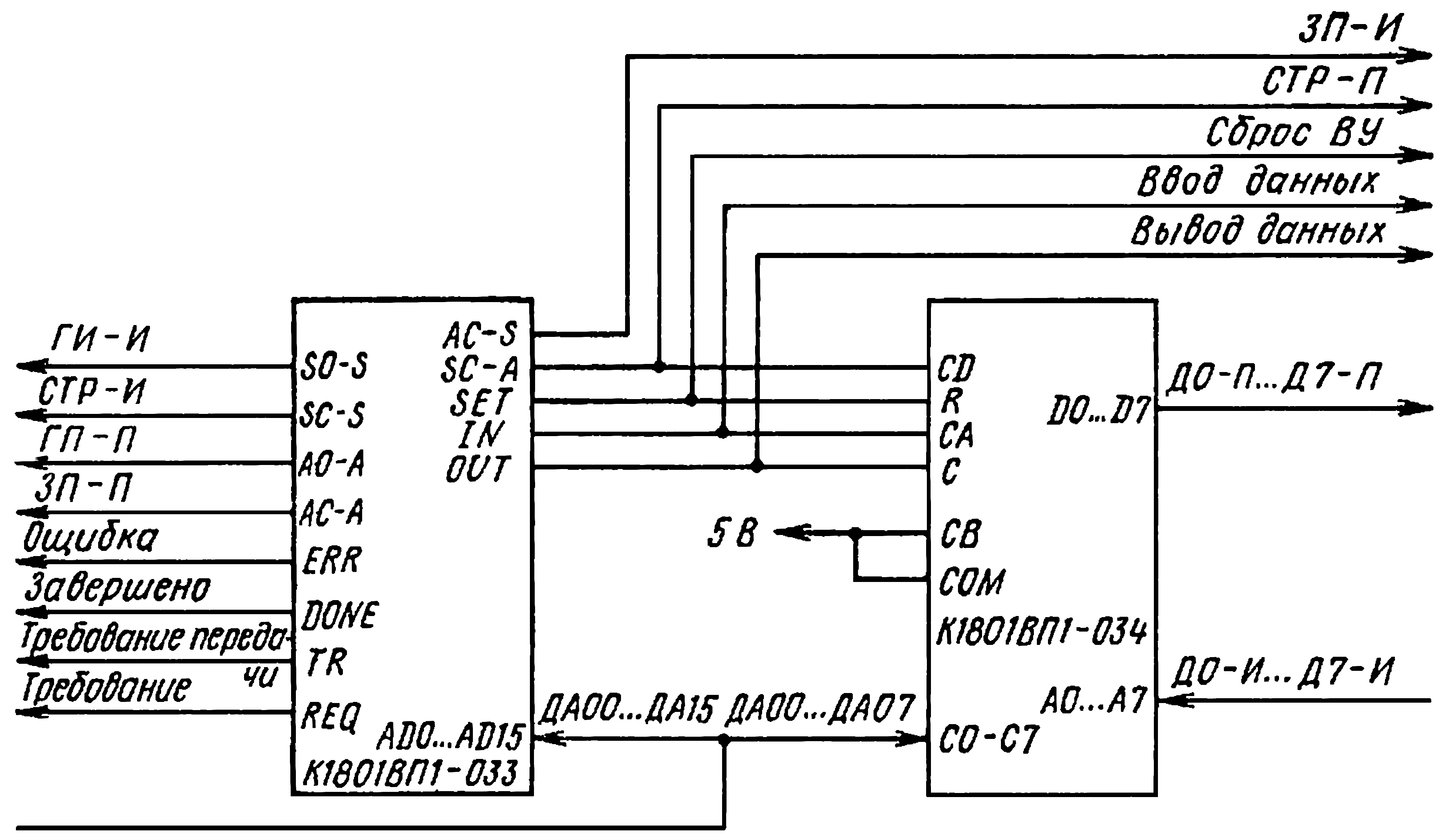

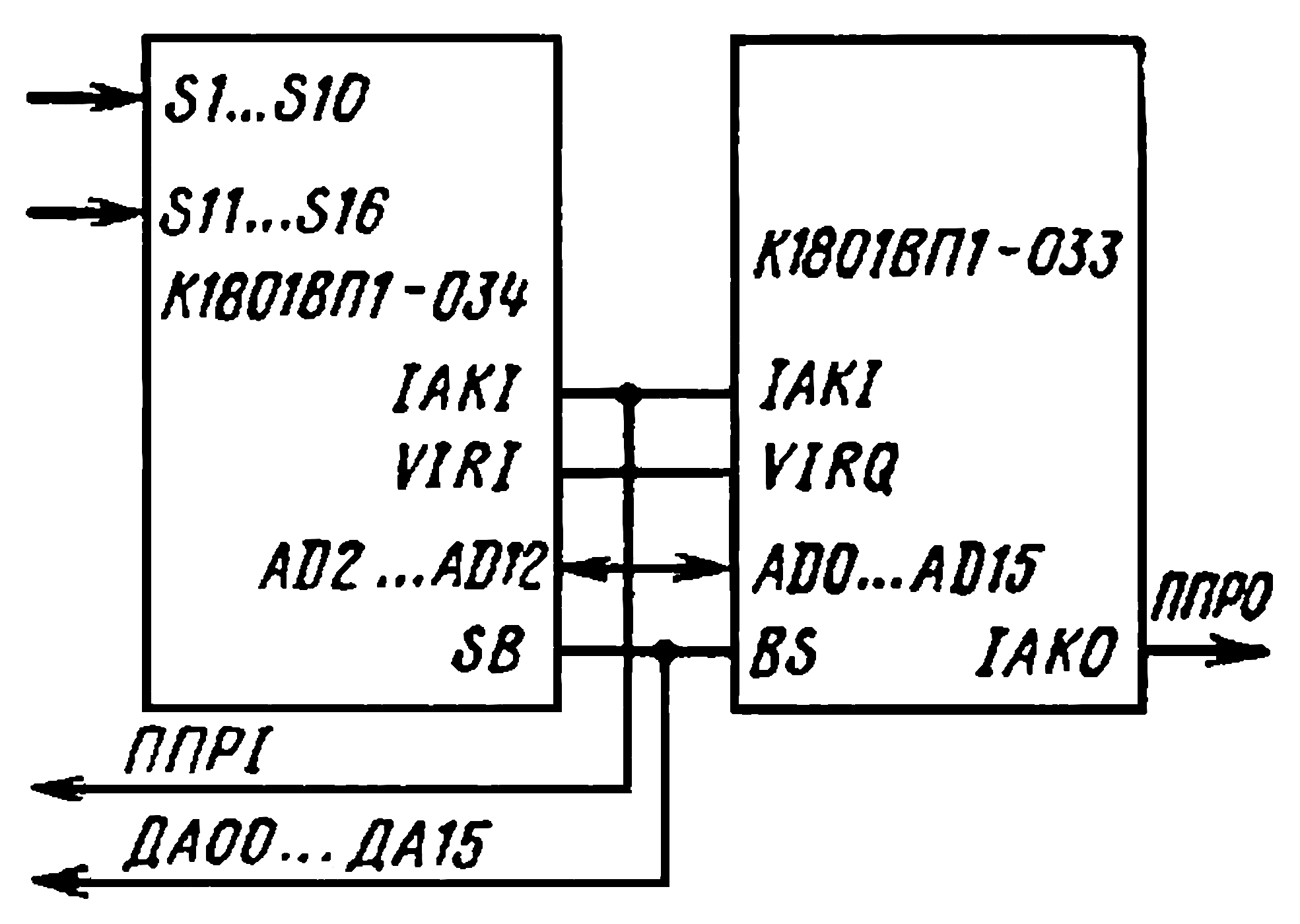

- Совместное применение микросхем К1801BП1-033 и К1801BП1-034 для построения интерфейсов параллельного ввода-вывода и байтового параллельного ввода-вывода, устройства выдачи вектора прерывания и компаратора адреса представлены на рис. 8 - 10 соответственно.

- Особенности применения микросхемы К1801ВП1-035

Группы адресов регистров и источников адресов прерываний задаются комбинаций уровней на выводах ACL0 и ACL1 (табл. 1). При заданной комбинации ACL0=1, ACL1 = 1 регистры микросхемы выбираются по адресу, состоящему из разрядов 1,2, и по сигналу BS. На разряды адреса 3...12 микросхема не реагирует. Группа 4 адресов может использоваться для внешнего произвольного набора адресов регистров и внешнего источника адресов векторов прерываний.

Форматы посылок по последовательному каналу задаются комбинацией уровней на входах NB0 и NB1 (табл. 2), скорость обмена - на входах FR0...FR3 (выводы 3...6) (табл. 3).

Режим работы с паритетом или без него, а также с паритетом по чётности или нечётности выбирается в зависимости от комбинации уровней на входах NP и PEV (выводы 30 и 32) (табл. 4).

Состояния выхода TF передатчика в зависимости от уровня на входе BSYD (вывод 29), наличия Лог. 1 в разряде 0 регистра состояний (PC) передатчика и подачи сигнала DCLO показаны в табл. 5.

Микросхема имеет выходы HALT (вывод 31), VIRQ (вывод 35) и RPLY (вывод 39) с открытым стоком, обеспечивающим только низкий уровень сигнала. Для формирования на этих выходах высокого уровня необходимо между ними и шиной источника питания 5 В включить резистор с номинальным значением, рассчитанным, исходя из величины выходного тока. Лог. 0 IOL, равного не более 3,2 мА.

Начальная установка микросхемы осуществляется подачей сигналов низкого уровня на входы INIT (вывод 34) и DCLO (вывод 40). Длительность сигналов на входе INIT - не менее 10 мкс, на входе DCLO - не менее 5 мс.

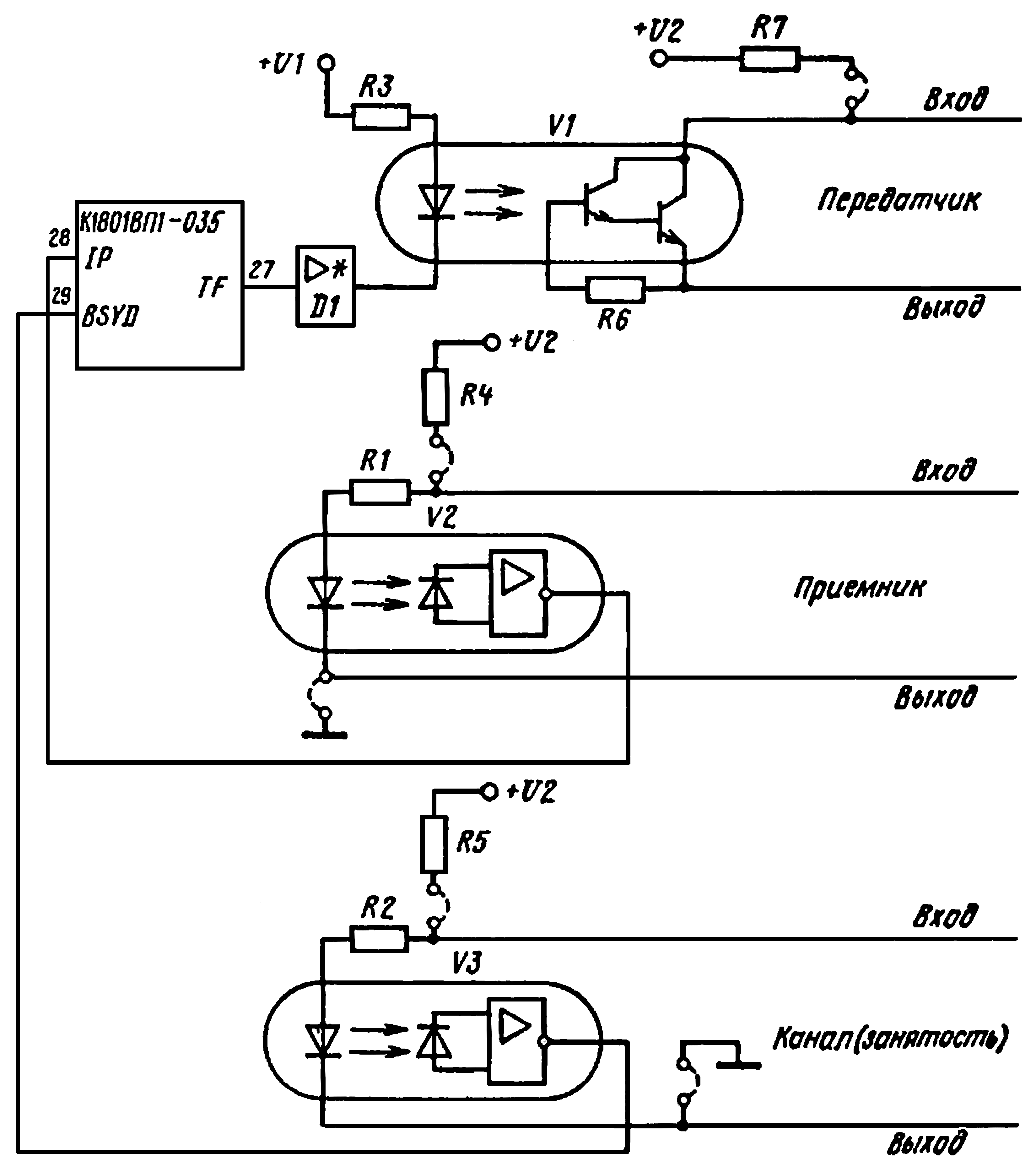

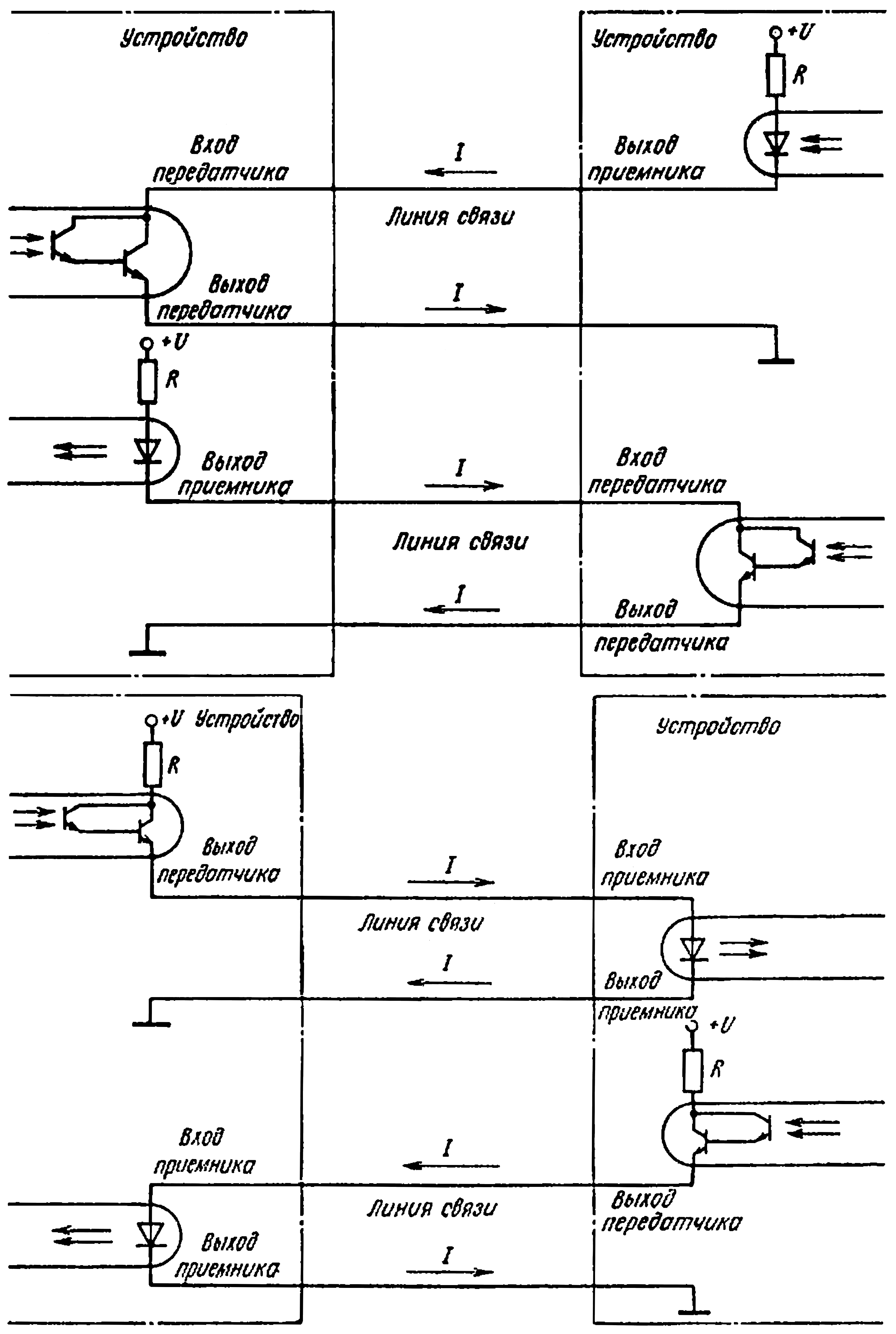

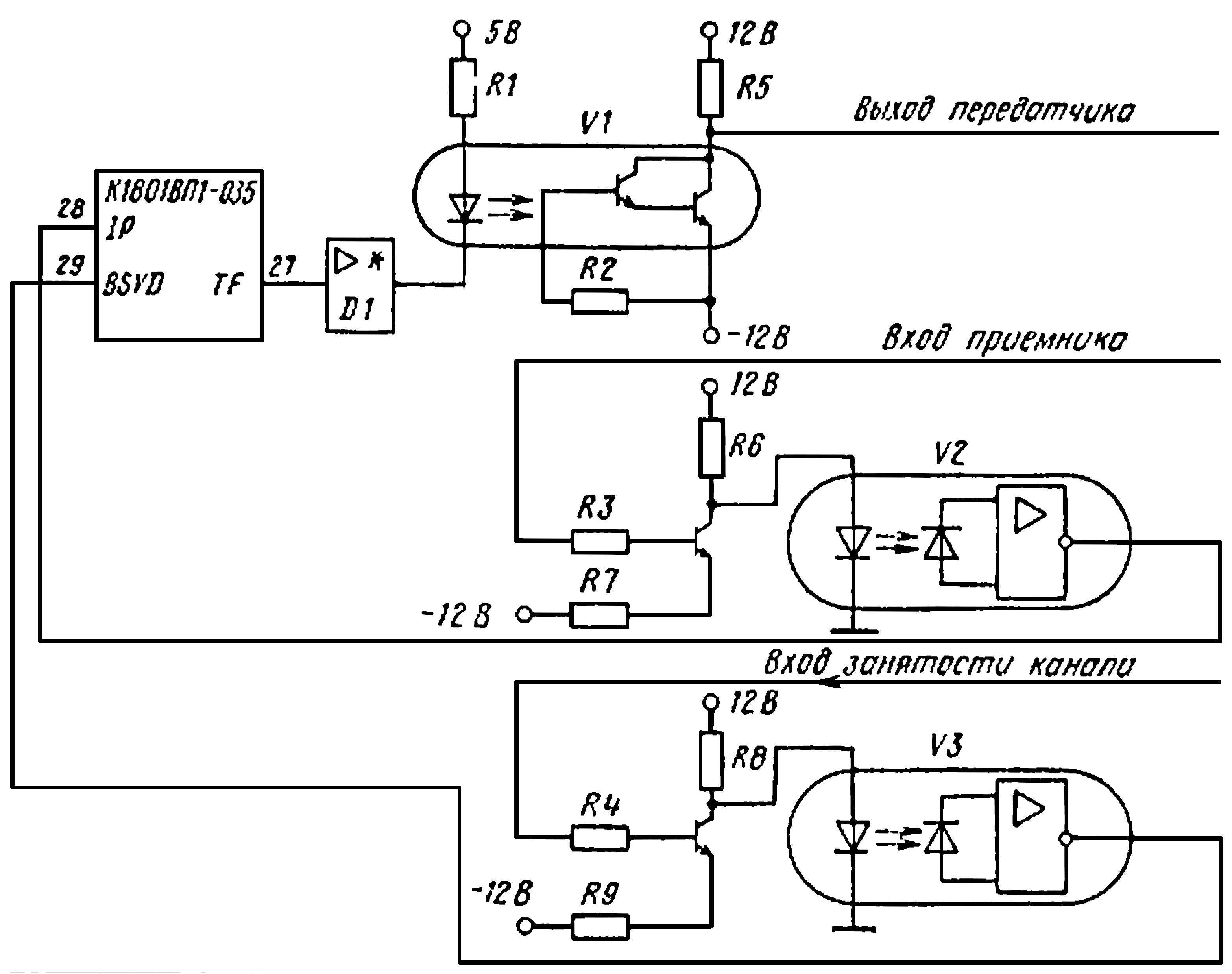

Для работы микросхемы со специальными последовательными линиями: токовыми петлями, телеграфным интерфейсом и другими, - необходимы специальные схемы поддержки. Сопряжение микросхемы с токовыми петлями (рис. 11) позволяет обеспечить ток 20 или 40 мА. При организации токовых петель схемы сопряжения, содержащие источники питания, являются активными, иначе, - пассивными. Организация токовых петель при активных приёмниках и пассивных передатчиках, при активных передатчиках и пассивных приёмниках представлена на рис. 12. Сопряжение микросхемы с телеграфным интерфейсом показано на рис. 13.

Г. Г. Глушкова

Рис. 1. Схема поддержки сигнала DOUT микропроцессора К1801BМ1

Рис. 2. Схема поддержки режима прямого доступа в память микропроцессора К1801BМ1: D2...D4 - К155ТМ2.

Рис. 3. Схема поддержки прерываний микропроцессора К1801BМ1: D1...D5 - К155ТМ2

Рис. 4. Схема поддержки сигнала RPLY микропроцессора К1801BМ1

Рис. 5. Схема поддержки сигналов SYNC и SACK микропроцессора К1801BМ1

Рис. 6. Схема управления блоком ОЗУ 16К 16-разрядных слов: если AD15=1, то RAS0; если AD15=0, то RAS1

Рис. 7. Схема управления блоком ОЗУ

Рис. 8. Интерфейс параллельного ввода-вывода

Рис. 9. Интерфейс байтового параллельного ввода-вывода

Рис. 10. Устройство выдачи вектора прерывания и компарации адреса

Рис. 11. Схема сопряжения микросхемы К1801ВП1-035 с токовыми петлями: V1 - оптрон АОТ1101; V2, V3 - оптроны К290ЛП1; D1 - микросхема с открытым коллектором; U2 - источник тока в петлях; R - токозадающие резисторы

Рис. 12. Схема организации токовых нетель при активных приёмниках и пассивных передатчиках и наоборот

Рис. 13. Схема сопряжения микросхемы К1801ВП1-035 с телеграфным интерфейсом 12 В: V1 - оптрон АОТ110А; V2, V3 - оптроны К293ЛП1; D1 - микросхема с открытым, коллектором

|

Обозначение |

Вывод |

Группа |

|||

|---|---|---|---|---|---|

|

1 |

2 |

3 |

4 |

||

|

ACL0 |

23 |

0 |

1 |

0 |

1 |

|

ACL1 |

24 |

0 |

0 |

1 |

1 |

Примечание. 0,1 - низкий и высокий уровни на входе.

|

Обозначение |

Вывод |

5 бит |

7 бит |

8 бит |

|---|---|---|---|---|

|

NB0 |

7 |

X |

0 |

1 |

|

NB1 |

8 |

0 |

1 |

1 |

Примечание. X - безразличное состояние.

|

Скорость обмена, Бод |

FR3 (вывод 6) |

FR2 (вывод 5) |

FR1 (вывод 4) |

FR0 (вывод 3) |

|---|---|---|---|---|

|

50 |

0 |

0 |

0 |

0 |

|

75 |

0 |

0 |

0 |

1 |

|

100 |

0 |

0 |

1 |

0 |

|

150 |

0 |

0 |

1 |

1 |

|

200 |

0 |

1 |

0 |

0 |

|

300 |

0 |

1 |

0 |

1 |

|

600 |

0 |

1 |

1 |

0 |

|

1200 |

0 |

1 |

1 |

1 |

|

2400 |

1 |

0 |

0 |

0 |

|

4800 |

1 |

0 |

0 |

1 |

|

9600 |

1 |

0 |

1 |

0 |

|

19 200 |

1 |

0 |

1 |

1 |

|

57 600 |

1 |

1 |

0 |

0 |

|

Режимы работы с паритетом |

NP (вывод 30) |

PEV (вывод 32) |

|---|---|---|

|

Нет формирования бита паритета и контроля паритета |

1 |

X |

|

Формирование бита чётности и контроль чётности |

0 |

1 |

|

Формирование бита нечётности и контроль нечётности |

0 |

0 |

|

Режим работы микросхемы и состояние линии |

Вход BSYD |

Наличие Лог 1 в разряде 0 PC передатчика |

Состояние выхода TF передатчика |

|---|---|---|---|

|

Выдача посылки, линия свободна |

0 |

Нет |

Выдача посылки |

|

Линия занята |

1 |

X |

0 (СТОП) |

|

«Разрыв» линии |

0 |

Есть |

1 (СТАРТ) |

|

Подача сигнала DCLO |

X |

X |

0 (СТОП) |