УДК 681.3.01 : 51

ИНТЕРФЕЙСНЫЕ БИС МИКРОПРОЦЕССОРНОГО КОМПЛЕКТА К1801[1]

Микропроцессорный комплект БИС серии К1801 наряду с однокристальными микропроцессорами [1,2] содержит ряд универсальных интерфейсных БИС для управления блоками оперативной памяти (К1801ВП1-030) и внешними устройствами (К1801ВП1-035), организации интерфейсных устройств параллельного ввода-вывода (К1801ВП1-033, К1801ВП1-034). Все интерфейсные БИС разработаны на основе базового матричного кристалла (БМК) К1801ВП1 с применением библиотечных элементов: инверторов, многовходовых элементов И-НЕ, ИЛИ-HE, триггеров и т.д. Собственно БМК состоит из ячеек трёх типов.

Изготовление БИС на основе БМК заключается в формировании с помощью двух верхних слоёв (слой металлизации и слой контактов) разветвлённых связей необходимой конфигурации между ячейками БМК. Процесс проектирования и изготовления БИС осуществляется в несколько этапов (техническое задание, ввод исходной информации, логическое моделирование, синтез тестов, трассировка связей, расчёт паразитных элементов связей, расчёт электрической схемы) с помощью автоматизированной системы проектирования. На основе БМК К1801ВП1 спроектировано несколько сотен различных заказных схем в основном частного применения, т. е. предназначенных для конкретной аппаратуры.

В разделе «Справочная информация» будут рассмотрены универсальные интерфейсные БИС, получившие наиболее широкое распространение:

- К1801ВП1-030 - устройство управления блоками ОЗУ динамического типа;

- К1801ВП1-033 - многофункциональное устройство, позволяющее реализовать интерфейс накопителя на гибких магнитных дисках, контроллер интерфейса параллельного ввода-вывода, контроллер байтового параллельного интерфейса;

- К1801ВП1-034 - многофункциональное устройство, предназначенное для организации устройства передачи данных, устройства выдачи вектора прерывания и компаратора адреса, буферного регистра данных;

- К1801ВП1-035 - контроллер внешних устройств, работающих на линию связи с последовательной передачей данных.

Все микросхемы изготавливаются по n-канальной МОП-технологии в керамических 42-выводных корпусах типа 429.42-5. Основные параметры микросхем приведены в табл. 1.

|

Параметр, единица измерения |

Обозначение |

Значение |

Температура, °C |

Режим измерения |

|

|---|---|---|---|---|---|

|

не менее |

не более |

||||

|

Выходное напряжение низкого уровня, В |

UOL |

- |

0,4 |

+25+10 |

UCC = 4,75 B |

|

|

- |

0,5 |

-10+3 +70+3 |

IOL = 3,2 мА |

|

|

Выходное напряжение высокого уровня, В |

UOH |

2,5 |

- |

+25+10 |

UCC = 4,75 B |

|

|

2.4 |

- |

-10+3 +70+3 |

IOH = 1,0 мА |

|

|

Ток утечки «Лог, 0» и «Лог. 1», мкА |

ILIL |

- |

1 |

+25+10 |

UCC = 5,25 B |

|

ILIH |

- |

10 |

+70+3 |

UIL = 0 B UIН = UCC |

|

|

Ток потребления, мА |

ICC |

- |

180 |

-10±3 |

UCC = 5,25 В |

|

|

- |

200 |

+70+3 |

UIL = 0 B UIH = UCC |

|

|

Напряжение питания, В |

UCC |

4,75 |

5,25 |

- |

- |

|

Ёмкость нагрузки, пФ |

CL |

- |

100 |

- |

- |

|

Длительность фронта выходного сигнала, нс |

tф |

- |

50 |

- |

CL = 100 пФ |

В этом номере журнала представлена микросхема К1801ВП1-030. Остальные интерфейсные БИС комплекта К1801 и рекомендации по их применению будут рассмотрены в последующих номерах.

Микросхема К1801ВП1-030

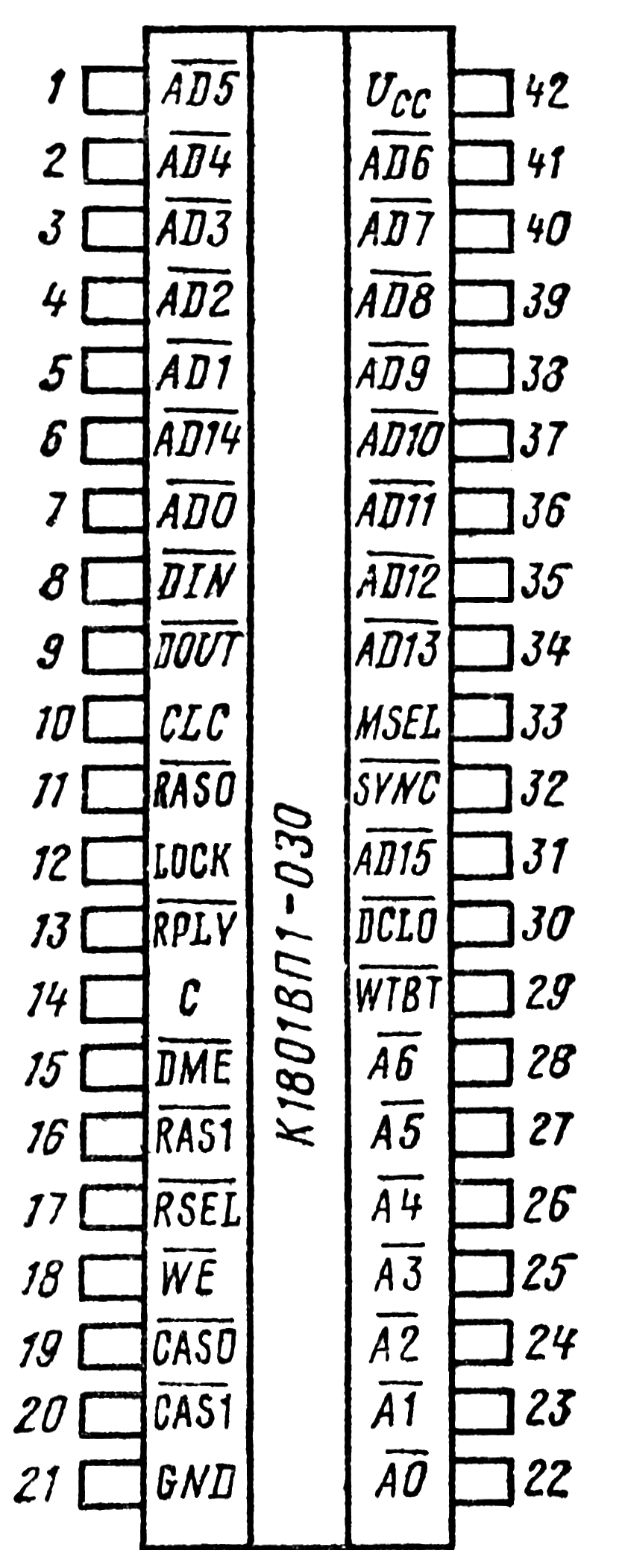

Предназначена для использования в блоках ОЗУ, выполненных на основе микросхем К565РУЗ с динамическим хранением данных, в качестве устройства управления (контроллера) обменом данных. Условное графическое обозначение микросхемы дано на рис. 1, назначение выводов приведено в табл. 2. Номер ТУ: оКО.348.740-0301 ТУ. Контроллер рассчитан на управление блоком ОЗУ ёмкостью 16К 16-разрядных слов, выполненном на 16 микросхемах серии К565РУЗ, или двумя полублоками. Микросхема осуществляет следующие функции:

- приём, хранение и преобразование адреса для накопителя ОЗУ;

- регенерацию памяти;

- обмен информацией по системной магистрали микро-ЭВМ «Электроника 60»;

- выработку вспомогательного сигнала блокирования LOCK при обращении в область внешних устройств (старшие 4К слов). Сигнал LOCK предназначен для использования БИС К1801ВП1-030 совместно с микропроцессором К1801ВМ1.

|

|

|

|

Рис. 1. Условное графическое обозначение микросхемы К1801ВП1-30 по порядку расположения (а) и функциональному назначению (б) выводов |

|

|

Вывод |

Обозначение |

Тип вывода |

Назначение |

|---|---|---|---|

|

1...5 |

AD5...AD1 |

Вход |

Адресные входы |

|

6 |

AD14 |

Вход |

Четырнадцатый разряд адреса-данных |

|

7 |

AD0 |

Вход |

Нулевой разряд адреса-данных |

|

8 |

DIN |

Вход |

Чтение данных |

|

9 |

DOUT |

Вход |

Запись данных |

|

10 |

CLC |

Вход |

Синхронизация |

|

11 |

RAS0 |

Выход |

Сигнал сопровождения адреса строки накопителя (1-ый полублок) |

|

12 |

LOCK |

Выход |

Блокировка |

|

13 |

RPLY |

Выход |

Ответ |

|

14 |

C |

Выход |

Сигнал стробирования записи в буферный регистр данных (БРД) |

|

15 |

DME |

Выход |

Выборка данных памяти |

|

16 |

RAS1 |

Выход |

Сигнал сопровождения адреса строки накопителя |

|

17 |

RSEL |

Вход |

Выборка регистра режима |

|

18 |

WE |

Выход |

Сигнал сопровождения записи в накопитель ОЗУ |

|

19 |

CAS0 |

Выход |

Сигнал сопровождения адреса колонки накопителя (1-й полублок) |

|

20 |

CAS1 |

Выход |

Сигнал сопровождения адреса колонки накопителя (2-й полублок) |

|

21 |

GND |

- |

Общий |

|

22 |

A0 |

Вход |

Нулевой разряд адреса накопителя ОЗУ |

|

23...28 |

A1...A6 |

Выходы |

Разряды адреса накопителя ОЗУ |

|

29 |

WTBT |

Вход |

Запись-байт |

|

30 |

DCLO |

Вход |

Авария источника питания |

|

31 |

AD15 |

Вход |

Пятнадцатый разряд адреса-данных магистрали |

|

32 |

SYNC |

Вход |

Обмен |

|

33 |

MSEL |

Вход |

Выборка памяти |

|

34...41 |

AD13...AD6 |

Входы |

Разряды адреса-данных |

|

42 |

UCC |

- |

Напряжение источника питания |

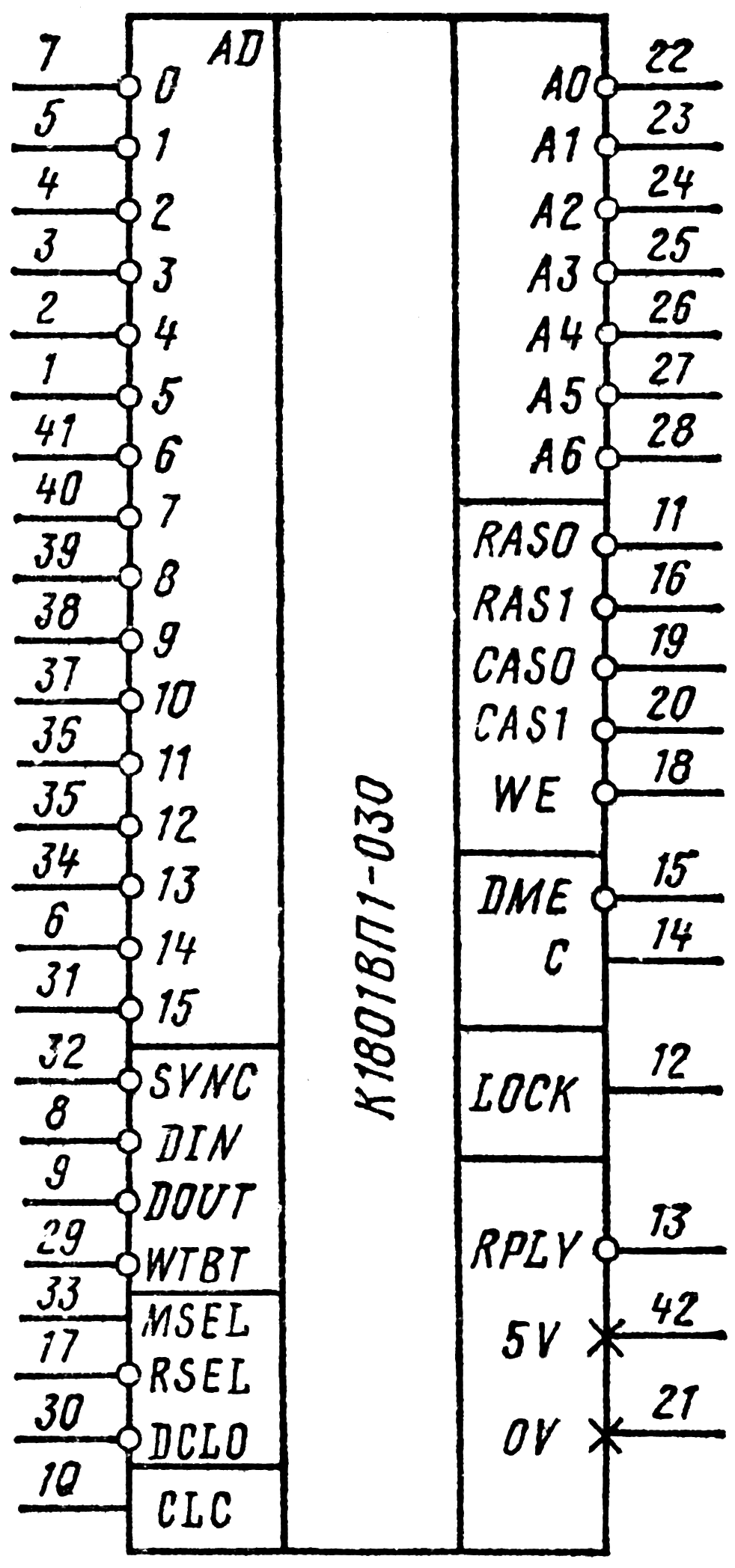

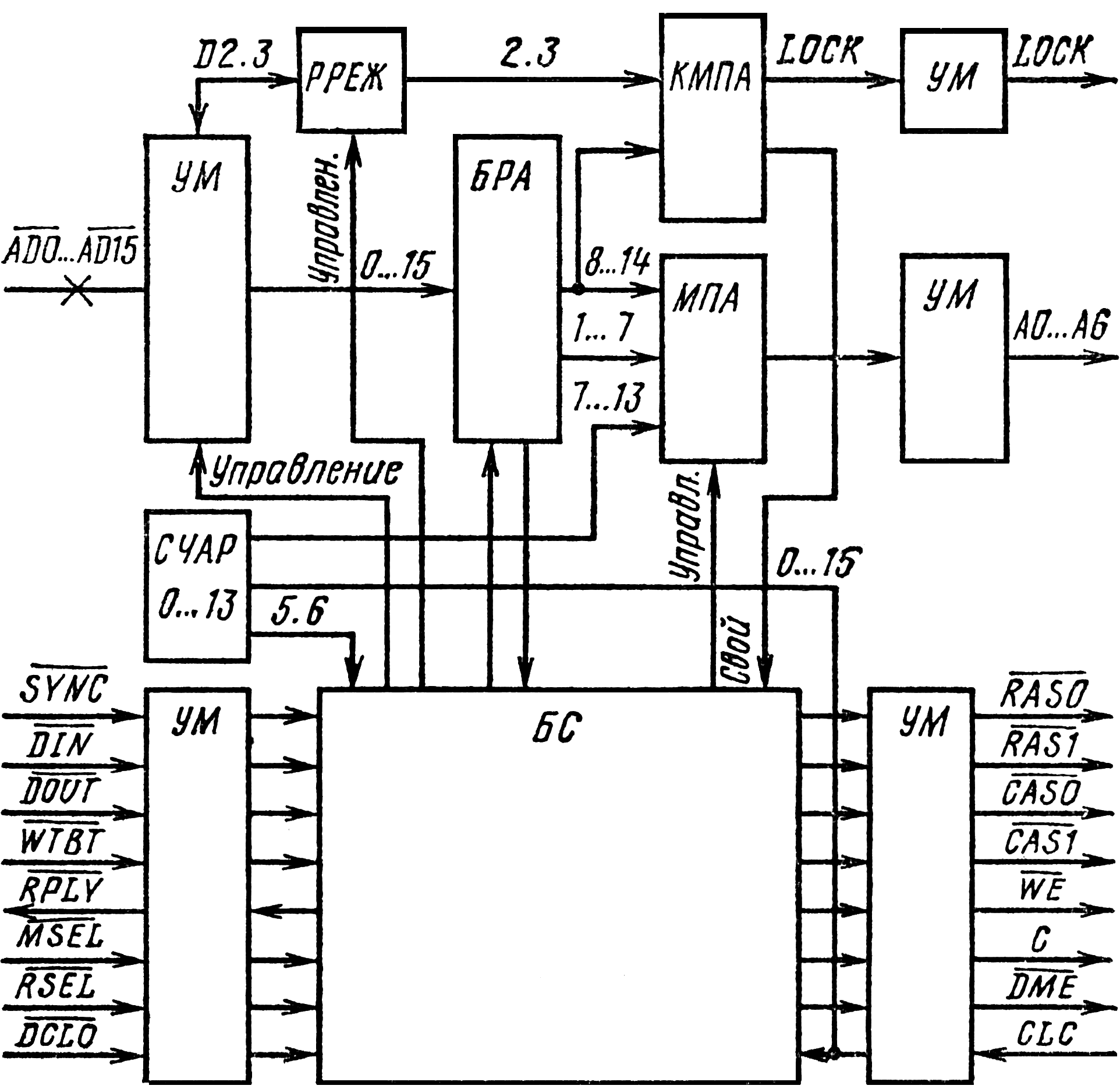

Структурная электрическая схема контроллера ОЗУ (рис. 2) включает счётчик адресов регенерации (СЧАР), буферный регистр адреса (БРА), мультиплексор адресов (МПА), регистр режима (РРЕЖ), компаратор адресов (КМПА), блок синхронизации (БС), буферные усилители мощности (УМ).

Рис. 2. Электрическая структурная схема микросхемы К1801ВП1-030

Счётчик адресов СЧАР объединяет 7-разрядный делитель тактовой частоты (разряды 0 ... 6) и собственно 7-разрядный счётчик адресов регенерации (разряды 7 ... 13). В режиме регенерации содержимое разрядов 7 ... 13 через мультиплексор поступает на выводы A0 ... A6 и является адресом регенерации.

Буферный регистр БРА (разряда 0...15) предназначен для хранения адреса, поступающего по системной магистрали' на выводы AD0 ... AD15. Содержимое разрядов 1 ... 7 в фазе выдачи адреса строки поступает через мультиплексор на выводы A0 ... A6 в режиме обмена.

Содержимое разрядов 8 ... 14 поступает на выводы A0 ... A6 в фазе выдачи адреса столбца и на компаратор для выработки сигнала LOCK. Содержимое разряда 0 используется в блоке синхронизации для определения номера байта при выполнении процедуры записи байта. Запись данных в БРА происходит высоким уровнем сигнала SYNC. Фиксируется запись низким уровнем этого сигнала.

Мультиплексор МПА служит для раздельной во времени выдачи адреса ОЗУ в виде 7-разрядных адресов строки и столбца в циклах обмена с накопителем ОЗУ, а также 7-разрядного адреса регенерации.

Вспомогательный регистр режима РРЕЖ предназначен для дублированного хранения служебных признаков режимов работы «останов» и «расширенная арифметика» микропроцессора К1801ВМ1. Содержит два разряда РРЕЖ2 и РРЕЖЗ, доступных по чтению и записи из канала (разряды AD2 и AD3 соответственно). Режиму «останов» соответствует значение единицы в разряде РРЕЖ2, режиму «расширенная арифметика» - в разряде РРЕЖЗ. Информация, хранимая в РРЕЖ, влияет на установку сигнала LOCK.

Компаратор адресов КМПА вырабатывает сигнал блокировки LOCK, который служит для выборки областей адресов из системного ПЗУ и блокировки этих областей в адресном пространстве внешних устройств.

Сигнал LOCK устанавливается в следующих случаях:

- адрес обращения находится в диапазоне 1600008 ... 1637778 (режим «останов»);

- адрес обращения - в диапазоне 1600008 ... 1737778 (режим «расширенная арифметика»);

- адрес обращения - в диапазоне 1730008 ... 1737778 (независимо от состояния режимов РРЕЖ2 и РРЕЖЗ).

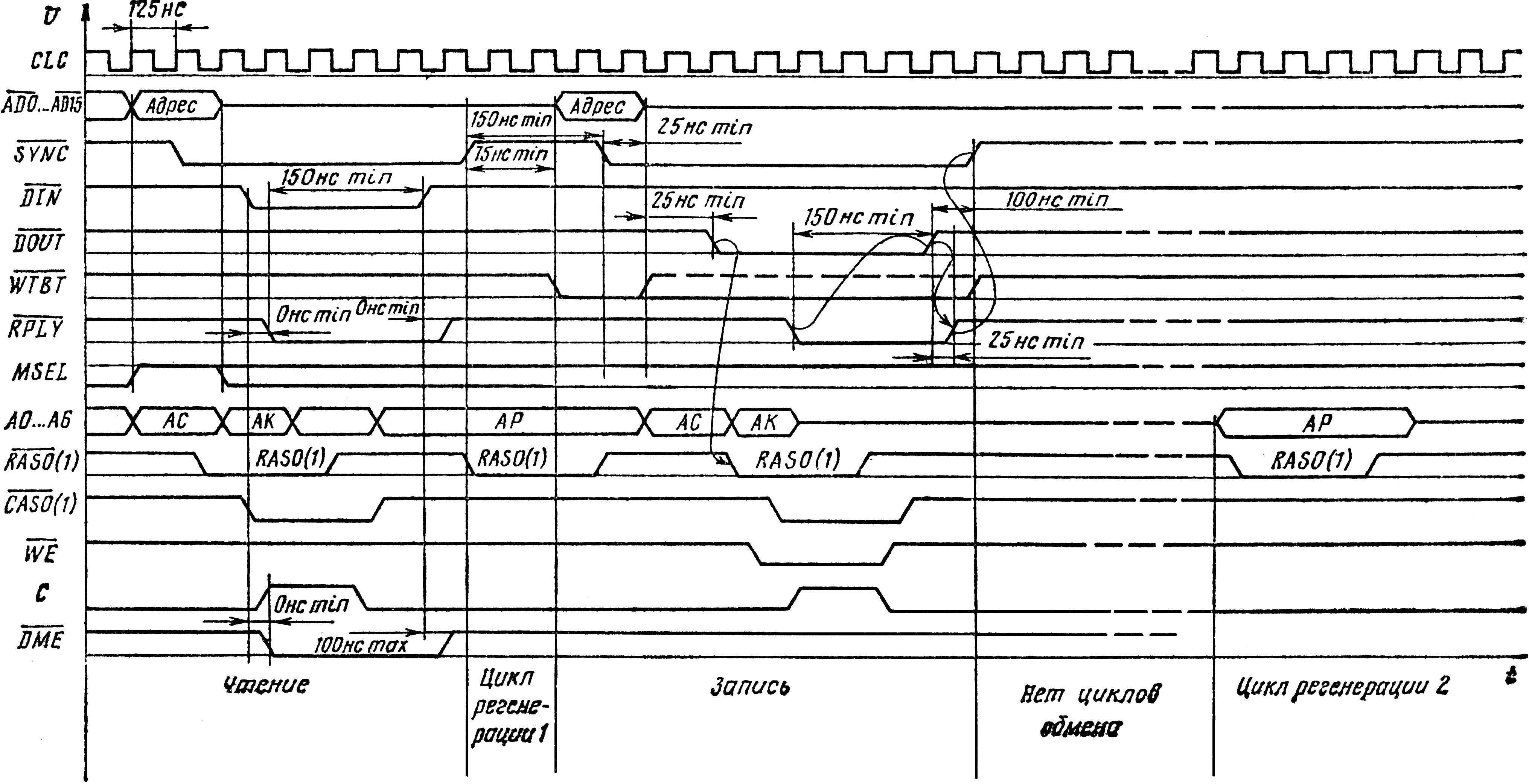

Рис. 3. Временная диаграмма работы микросхемы управления ОЗУ К1801ВП1-030

Компаратор вырабатывает признак «свой» для блока синхронизации при обращении по адресу в диапазоне 1776008... 1776778, который позволяет осуществлять запуск БС в отсутствие сигнала MSEL.

Блок синхронизации БС вырабатывает сигналы управления внутренними узлами микросхемы, накопителем ОЗУ, внешним буферным регистром данных, а также отрабатывает сигнал управления по системной магистрали ЭВМ.

Режим работы контроллера

Регенерация (восстановление) информации в памяти динамического типа происходит по принципу: один цикл регенерации - по одному адресу строки в течение 15,6 мкс. Полная регенерация по всем адресам наступает через 2 мс. В БС введена схема подсинхронизации запуска текущего цикла регенерации к окончанию цикла обмена информацией (цикл регенерации 1), что делает память динамического типа максимально прозрачной для процессора (рис. 3). При отсутствии циклов обмена с памятью в течение 8 мкс после получения БС запроса на регенерацию очередной цикл регенерации наступает принудительно, без подсинхронизации (цикл регенерации 2).

Сигналы RAS0 и RAS1 вырабатываются одновременно.

Чтение из памяти возможно при воздействии сигналов SYNC, задающих адрес обращения AD0... AD15 в буферном регистре и MSEL, которые фиксируются в элементах хранения БС. Кроме того, цикл чтения наступает при отсутствии сигнала WTBT в адресной части и отсутствии очередного цикла регенерации памяти.

Временная диаграмма работы БИС К1801ВП1-030 в режиме чтения показана на рис. 3. Выходные сигналы DME и RPLY микросхема вырабатывает только при наличии сигнала DIN. Сигнал RAS0 устанавливается в фазе выдачи адреса, если AD15=1. При AD15=0 формируется сигнал RAS1. Сигналы CAS0 и CAS1 вырабатываются одновременно.

Запись в память вызывают следующие сигналы:

- SYNC, фиксирующий адрес обращения AD0 ... AD15 в БРА;

- MSEL и WTBT, которые фиксируются в элементах хранения БС;

- сигнал DOUT, а также отсутствие очередного цикла регенерации памяти.

Временная диаграмма работы контроллера в режиме записи так же приведена на рис. 3.

Наличие сигнала WTBT в фазе выдачи адреса является признаком записи слова, а в фазе выдачи данных - признаком записи байта. При модификации «запись байта» БС вырабатывает сигнал CAS0, если AD0=1 в фазе выдачи адреса. Если AD0=0, устанавливается сигнал CAS1. При модификации «запись слова» сигналы CAS0 и CAS1 вырабатываются одновременно.

Блокировка. Сигнал блокировки устанавливается в фазе выдачи адреса. Задержка сигнала относительно момента выдачи адреса на выводы AD0 ... AD15 - не более 100 нс.

Начальная установка. Микросхема приходит в состояние готовности за время, соответствующее длительности прохождения семи синхронизирующих импульсов CLC. Сигнал DCLO устанавливает СЧАР в нулевое состояние и РРЕЖ в режим «останов».

ЛИТЕРАТУРА

- Однокристальные микропроцессоры комплекта БИС серии К1801 / В.Л. Дшхунян, Ю.И. Борщенко, В.Р. Науменков и др. // Микропроцессорные средства и системы. - 1984. - № 4. - С. 12.

- Однокристальный микропроцессор КМ1801ВМ3 / Р.И. Волков, В.П. Горский, В.Л. Дшхунян и др. // Микропроцессорные средства и системы. - 1986. - № 4, - С. 37.

Тел. 208-73-23, Москва, Г. Г. Глушкова

[1] Цикл статей, рассчитанный на публикацию с продолжением в последующих номерах журнала в разделе «Справочная информация».