УДК 681.3.01 : 51

ИНТЕРФЕЙСНЫЕ БИС МИКРОПРОЦЕССОРНОГО КОМПЛЕКТА К1801: МИКРОСХЕМА К1801ВП1-035

(Продолжение цикла. Начало в № 4 - 6, 1988)

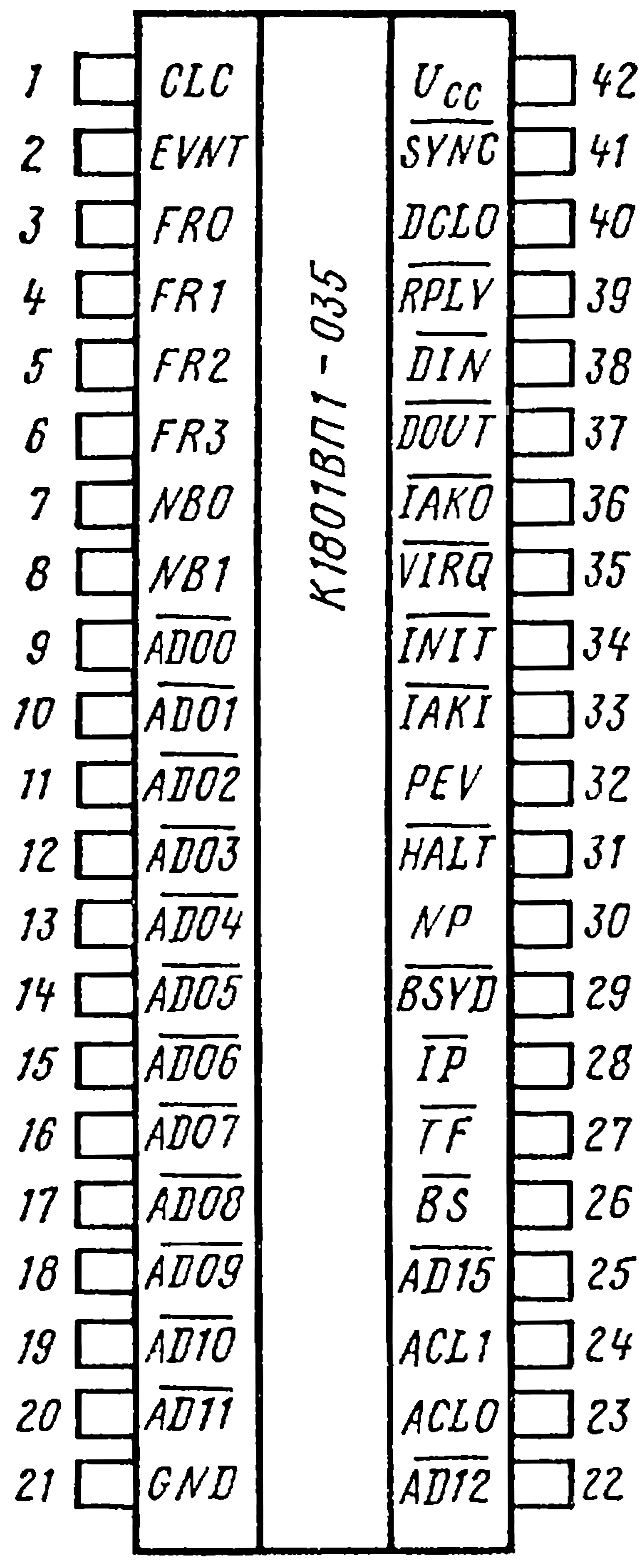

Микросхема К1801ВП1-035 (асинхронный приёмник-передатчик), выполненная по n-канальной МОП-технологии, является однокристальным контроллером внешних устройств, работающих на линии связи с последовательной передачей информации в дуплексном режиме, и предназначена для преобразования параллельной информации в последовательную и наоборот. Кристалл содержит около 5000 транзисторов и помещён в 42-выводной планарный металлокерамический корпус. Условное графическое обозначение микросхемы приведено на рис. 1, назначение выводов показано в табл. 1.

В режиме обмена информацией по последовательному каналу микросхема обеспечивает требования интерфейса для радиального подключения устройств с последовательной передачей информации (ИРПС). В составе ЭВМ она может использоваться для связи процессора с отдалёнными устройствами, в частности с пультовым терминалом.

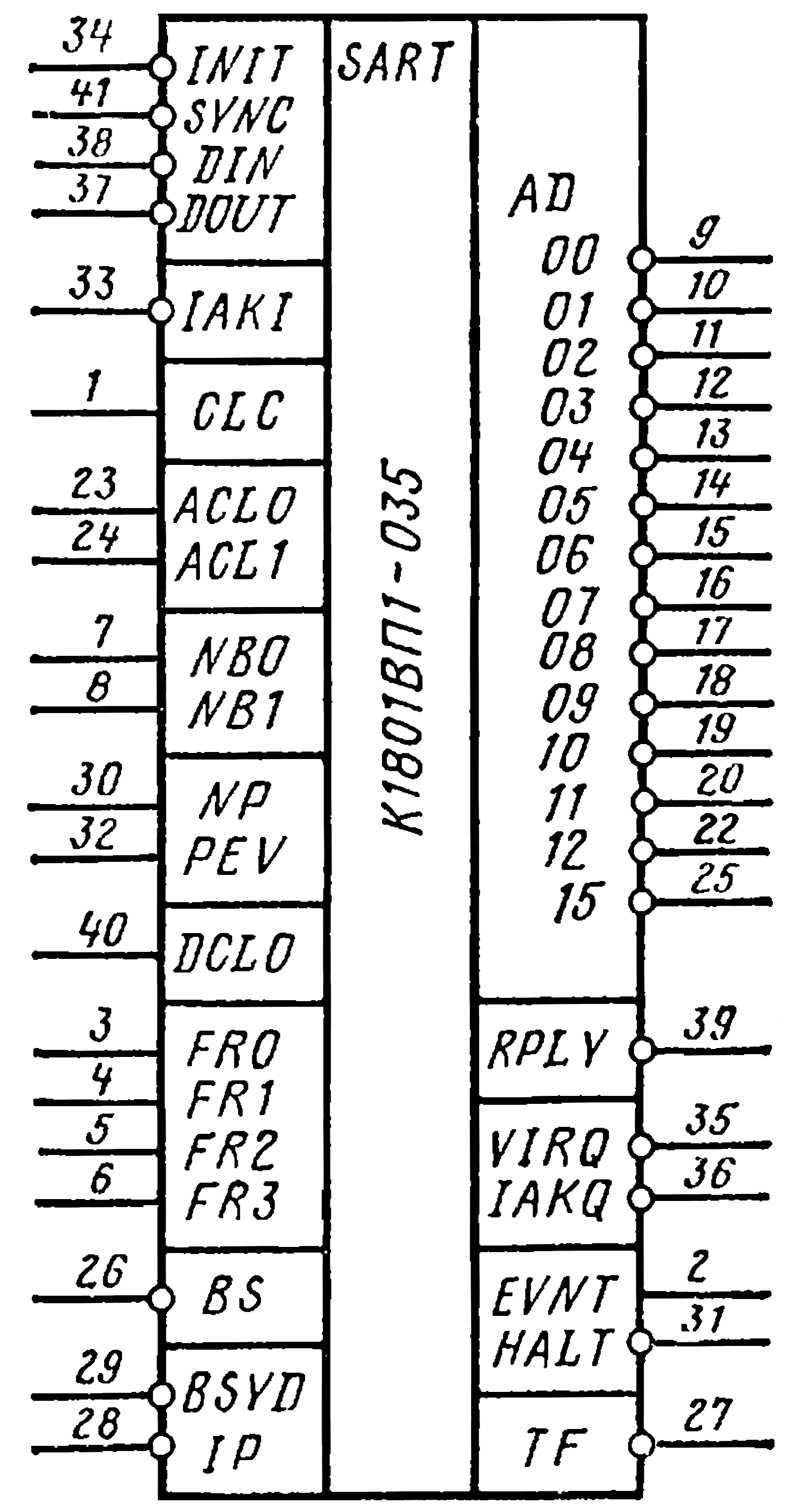

Микросхема состоит из следующих основных функциональных блоков (рис. 2):

- блока системной магистрали, обеспечивающего связь параллельного канала и регистров микросхемы для записи информации (адресов и данных) в регистры, а также чтения информации из регистров или чтения векторов прерываний;

- блока синхронизации для записи и чтения информации из регистров и синхронизации работы микросхемы по системной магистрали;

- компаратора адресов и управляющих сигналов, предназначенных для выбора по адресу регистров микросхемы и выработки сигналов записи или чтения;

- блока режимов работы, поддерживающего работу микросхемы по последовательному каналу в различных форматах данных, а также с паритетом пли без него;

- блоков приёмника и передатчика, включающих регистры состояния, сдвиговый, буферный и параллельный;

- блока селектора скоростей, обеспечивающего работу микросхемы на разных скоростях обмена информацией по последовательному каналу, а также выработку сигнала EVNT частотой 50 Гц.

|

|

Рис. 1. Условное графическое обозначение микросхемы К1801ВП1-035 по порядку расположения (а) и функциональному назначению (б) выводов |

|

Вывод |

Обозначение |

Тип |

Наименование |

|---|---|---|---|

|

1 |

CLC |

Вход |

Тактовая частота |

|

2 |

EVNT |

Выход |

Прерывания по таймеру 50 Гц |

|

3...6 |

FR0...FR3 |

Вход |

Выбор скорости обмена |

|

7,8 |

NB0, NB1 |

Вход |

Выбор формата |

|

9...20 |

AD00...AD11 |

Вход-выход, вход |

Разряды адреса-данных |

|

21 |

GND |

- |

Общий |

|

22 |

AD12 |

Вход-выход |

Двенадцатый разряд адреса-данных |

|

23 |

ACL0 |

Вход |

Выбор адреса |

|

24 |

ACL1 |

Вход |

|

|

25 |

AD15 |

Выход |

Пятнадцатый разряд адреса-данных |

|

26 |

BS |

Вход |

Выбор внешнего устройства |

|

27 |

TF |

Выход |

Сигнал передатчика |

|

28 |

IP |

Вход |

Сигнал приёмника |

|

29 |

BSYD |

Вход |

Сигнал занятости последовательного канала |

|

30 |

NP |

Вход |

Установка паритета |

|

31 |

HALT |

Выход |

Останов |

|

32 |

PEV |

Вход |

Установка чётности или нечётности |

|

33 |

IAKI |

Вход |

Сигнал предоставления прерывания по каналу |

|

34 |

INIT |

Вход |

Установка системной магистрали |

|

35 |

VIRQ |

Выход |

Требование векторного прерывания |

|

36 |

IAKO |

Выход |

Предоставление прерывания системной магистрали |

|

37 |

DOUT |

Вход |

Вывод данных |

|

38 |

DIN |

Вход |

Ввод данных |

|

39 |

RPLY |

Выход |

Ответ |

|

40 |

DCLO |

Вход |

Авария источника питания |

|

41 |

SYNC |

Вход |

Обмен |

|

42 |

Uсс |

- |

Напряжение источника питания |

Рис. 2. Электрическая структурная схема устройства последовательного ввода-вывода

Скорости обмена информацией при работе по последовательному каналу с частотой 4608 кГц составляют 50, 75, 100, 150, 200, 300, 600, 1200, 2400, 4800, 9600, 19200 бод. Приём и выдача посылки осуществляются в форматах 5, 7 или 8 информационных битов. Микросхема обеспечивает формирование двухстоповых и приём полуторастоповых битов (в формате посылки 5 бит), а также формирование и контроль бита паритета (чётности или нечётности) и работу без бита паритета.

Микросхема содержит четыре регистра и два источника адресов вектора прерывания. Адреса регистров и векторов - сменные по группам (табл. 2).

|

Регистры, источник адреса |

Группа |

|||

|---|---|---|---|---|

|

1 |

2 |

3 |

4 |

|

|

Регистр состояния приёмника |

177560 |

176560 |

176570 |

XXXXX0 |

|

Буферный регистр приёмника |

177562 |

176562 |

176572 |

ХХХХХ2 |

|

Регистр состояния передатчика |

177564 |

176564 |

176574 |

ХХХХХ4 |

|

Буферный регистр передатчика |

177566 |

176566 |

176576 |

ХХХХХ6 |

|

Адрес вектора прерывания приёмника |

060 |

360 |

370 |

XX0 |

|

Адрес вектора прерывания передатчика |

064 |

364 |

374 |

ХХ4 |

Форматы регистров

Регистр состояния приёмника (рис. 3).

|

15 |

|

|

12 |

|

|

|

|

7 |

6 |

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3. Формат регистра состояния приёмника

Разряды 0...5, 8...11, 13, 14 не используются и читаются как Лог. 0.

Разряд 6 - разрешение работы приёмника по прерыванию. Если этот разряд установлен в состояние Лог. 1, то прерывание разрешено, если - в состояние Лог. 0, то запрещено. Сбрасывается в Лог. 0 по сигналу INIT. Доступен по записи и чтению.

Разряд 7 - флаг состояния приёмника. Устанавливается в Лог. 1 при поступлении посылки в буферный регистр приёмника от предыдущей посылки или от исходного состояния СТОП на линии при включении источника питания после приёма первой посылки. Сбрасывается в Лог. 0 по окончании чтения посылки буферного регистра приёмника или по сигналу INIT. Доступен по чтению.

Разряд 12 - ошибка переполнения. Устанавливается в Лог. 1, если в сдвиговый регистр приёмника поступило более одной посылки без чтения из буферного регистра приёмника первой поступившей посылки. При этом независимо от числа поступивших в канал приёмника посылок в буферном регистре сохраняется первая посылка. Разряд 12 находится в состоянии Лог. 0, если поступившая в буферный регистр посылка читается до окончания поступления в сдвиговый регистр последнего информационного бита следующей посылки. Сбрасывается в Лог. 0 по окончании чтения буферного регистра приёмника или по сигналу INIT. Доступен по чтению.

Разряд 15 - ошибка в принятой посылке. Устанавливается в состояние Лог. 1, если есть ошибка паритета в принятой посылке и установлено условие контроля паритета. Находится в состоянии Лог. 0, если нет ошибки паритета или не установлено условие контроля паритета. Сбрасывается в Лог. 0 по чтению буферного регистра приёмника или по сигналу INIT. Доступен по чтению.

Буферный регистр приёмника (рис. 4)

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 4. Формат буферного регистра приёмника

Разряды 0...7 содержат посылку, принятую с линии. В разряде 0 находится первый бит, в разряде 7 - восьмой бит посылки. При установленном контроле паритета в следующем за последним битом посылки находится бит паритета. При формате 8 бит он анализируется микросхемой, но в буферный регистр не поступает.

Низкий уровень бита в посылке на входе IP соответствует Лог. 1, высокий уровень - Лог. 0 в буферном регистре приёмника. Разряды 8...15 не используются и читаются как Лог. 0. Регистр доступен по чтению.

Регистр состояния передатчика (рис. 5)

|

15 |

|

|

|

|

|

|

8 |

7 |

6 |

|

|

|

2 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5. Формат регистра состояния передатчика

Разряд 0 - разрыв линии. Если он находится в состоянии Лог. 1, то на выходе TF устанавливается высокий уровень (состояние СТАРТ) при условии, что на входе BSYD - низкий уровень. Если на входе BSYD высокий уровень, то на выходе TF устанавливается низкий уровень (состояние СТОП). Установка разряда 0 в состояние Лог. 1 этот уровень не изменяет. Разряд 0 доступен по записи и чтению.

Разряд 2 - проверка работы. Если этот разряд установлен в состояние Лог. 1, то выдаваемая с выхода TF посылка поступает также и на канал приёмника. При этом вход IP для приёма посылок с линии закрыт. Разряд 2 доступен по записи и чтению.

Разряд 6 - разрешение работы передатчика по прерыванию. Если этот разряд установлен в состояние Лог. 1, то прерывание разрешено, если в Лог. 0, то запрещено. Доступен по записи и чтению.

Разряд 7 - флаг состояния передатчика. Устанавливается в Лог. 1 по началу выдачи посылки на линию или по сигналу DCLO. Сбрасывается в Лог. 0 по записи данных в буферный регистр передатчика. Если разряд 7 установлен в Лог. 1, то буферный регистр передатчика будет пуст. Если запись данных в буферный регистр произошла во время выдачи посылки, то следующая посылка начинается сразу же по окончании предыдущей. Доступен по чтению.

Разряды 1, 3...5, 8... 15 не используются и читаются как Лог. 0.

Буферный регистр передатчика (рис. 6).

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 6. Формат буферного регистра передатчика

Разряды 0...7 содержат данные для передачи посылки на линию. В разряд 0 записывается первый бит, в разряд 7 - восьмой бит посылки. По окончании записи в этот регистр происходит запись данных в сдвиговый регистр передатчика. При условии низкого уровня на входе BSYD посылка с выхода TF поступает на линию. Бит паритета автоматически следует за последним битом посылки при условии работы с контролем чётности или нечётности. Этот бит формируется на выходе TF низким уровнем при записи Лог. 1. и высоким уровнем при записи Лог. 0.

В режиме чтения по адресу буферного регистра передатчика читается адрес источника вектора прерывания. Разряды 8... 15 читаются как Лог. 0.

Режим прерывания

Прерывание от приёмника. Запрос на прерывание от приёмника возникает, если разряды 6 и 7 регистра состояния приёмника установлены в 1. При обработке запроса на прерывание читается адрес вектора прерывания приёмника.

Прерывание от передатчика. Запрос на прерывание от передатчика возникает, если разряды 6 и 7 регистра состояния передатчика установлены в 1. При обработке запроса на прерывание читается адрес вектора прерывания передатчика.

Формат источников адресов векторов прерываний (рис. 7)

|

15 |

|

|

|

|

|

|

8 |

7 |

|

|

|

3 |

2 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 7. Формат источников адресов векторов прерываний

Разряд 2 - указатель адреса вектора прерывания. Запись 0 в разряд 2 указывает на адрес вектора прерывания приёмника, 1 - передатчика. Разряды 3...7 - сменная часть адреса вектора прерывания. Они читаются как Лог. 0. если выбрана четвертая группа адресов регистров и источников адресов векторов прерываний. Разряды 0, 1, 8... 15 не используются, читаются как Лог. 0.

Приоритет запроса от приёмника выше приоритета запроса от передатчика.

По окончании приёма посылки при отсутствии сигнала СТОП (разрыв линии) на выходе HALT устанавливается низкий уровень. Высокий уровень на этом выходе возникает по сигналу INIT. При тактовой частоте 4608 кГц на выходе EVNT формируются импульсные сигналы со скважностью Q=2 и частотой 50 Гц.

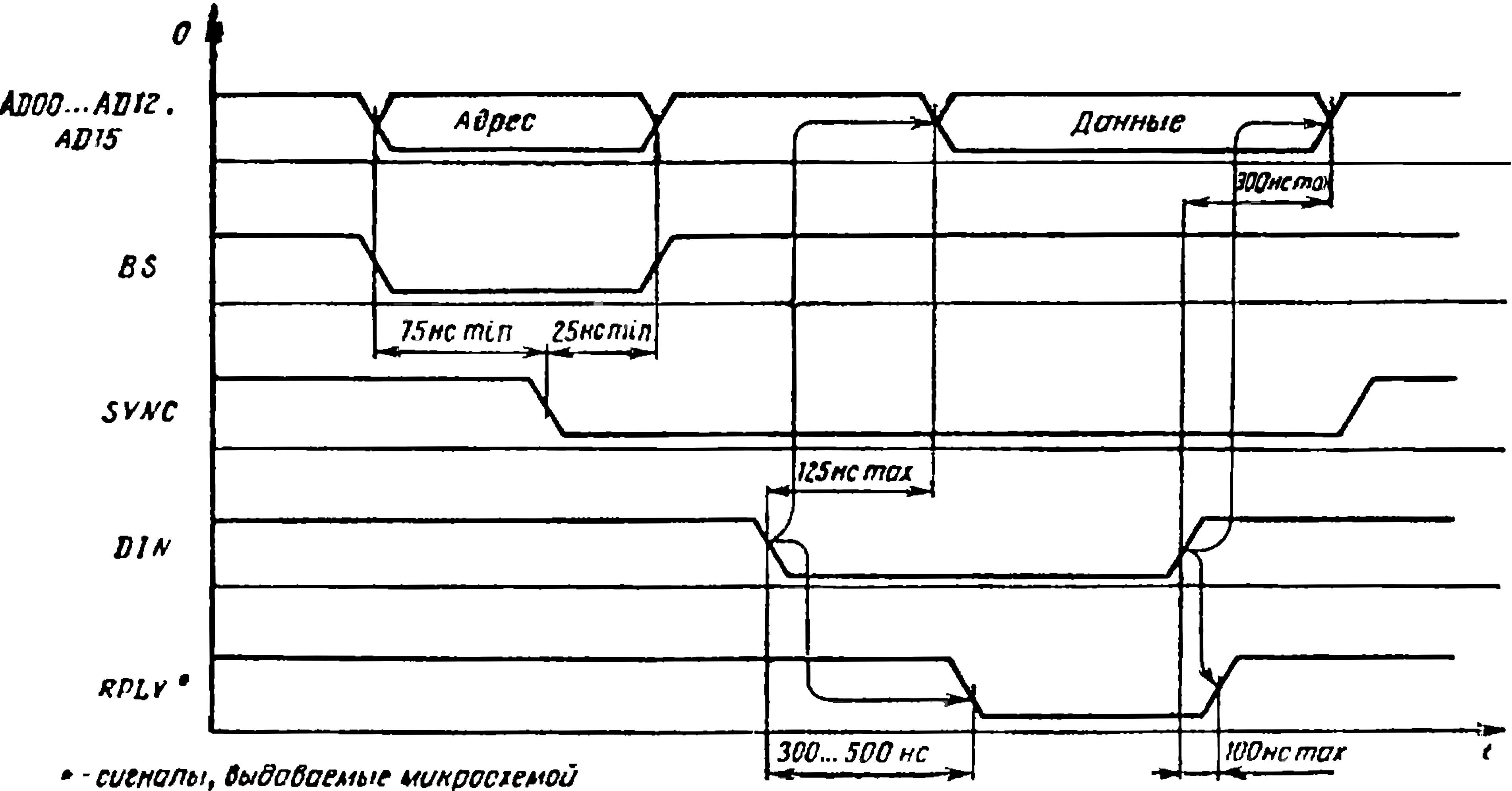

Работа микросхемы

Связь микросхемы с процессором осуществляется по каналу МПИ.

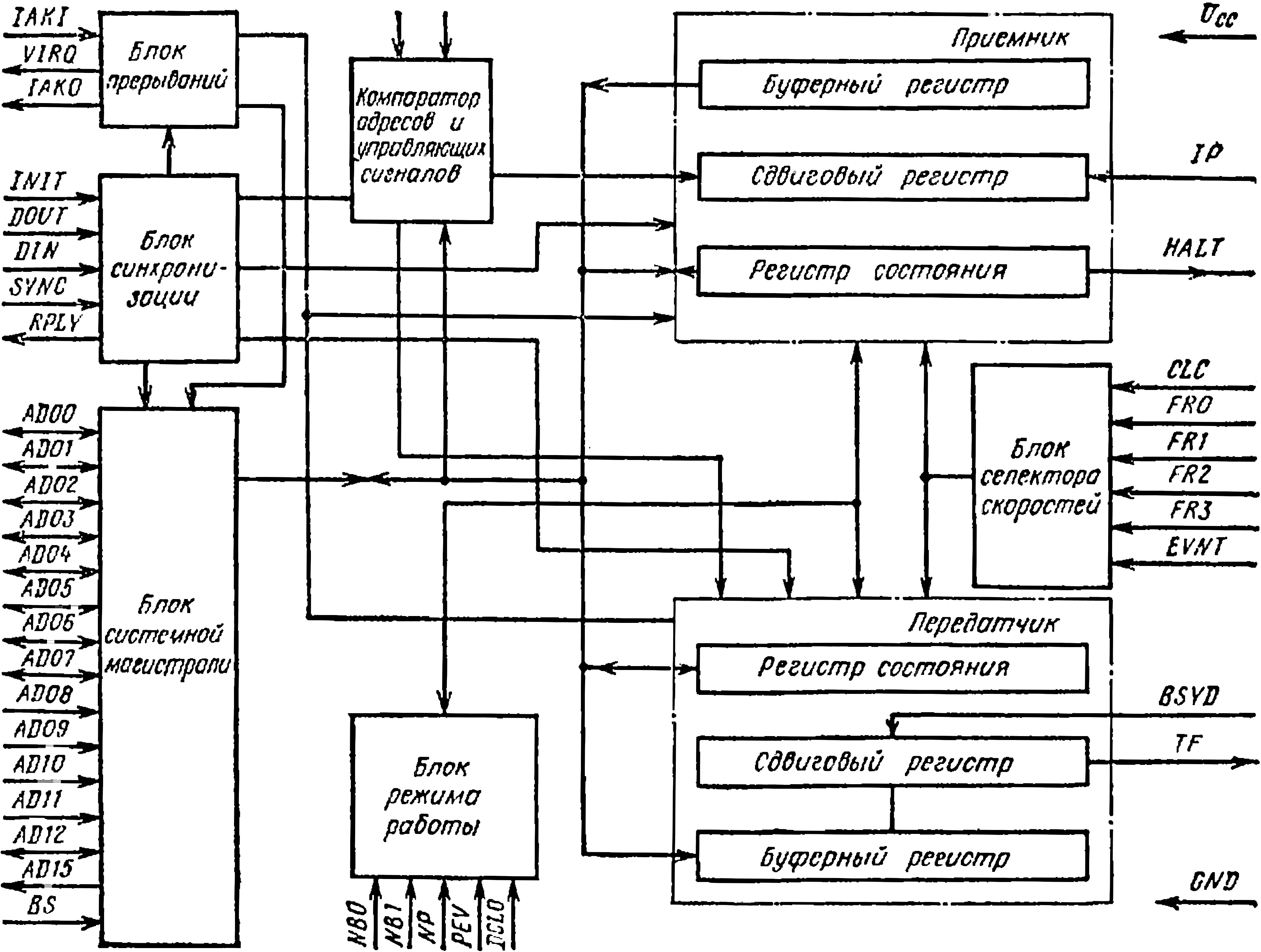

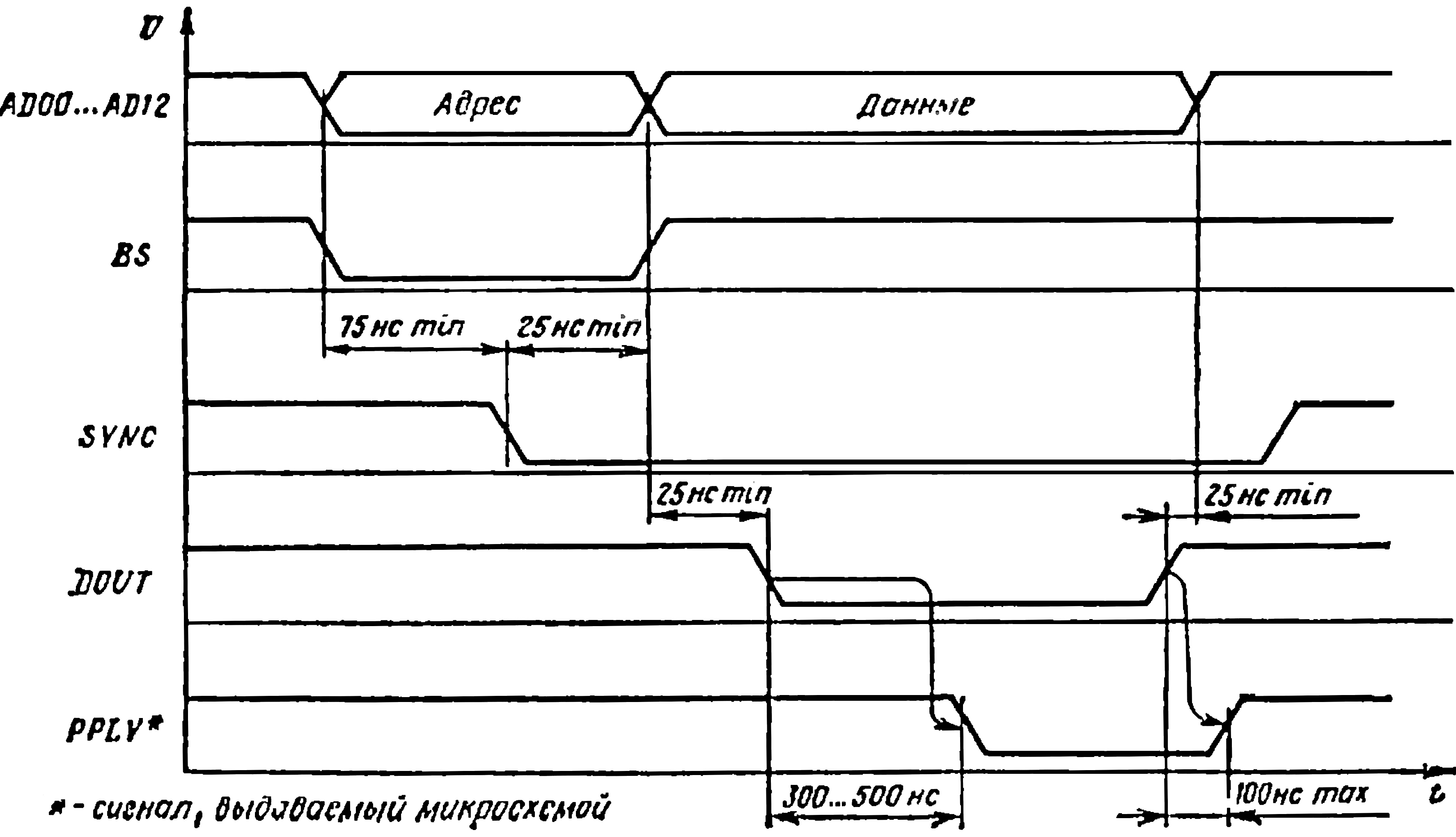

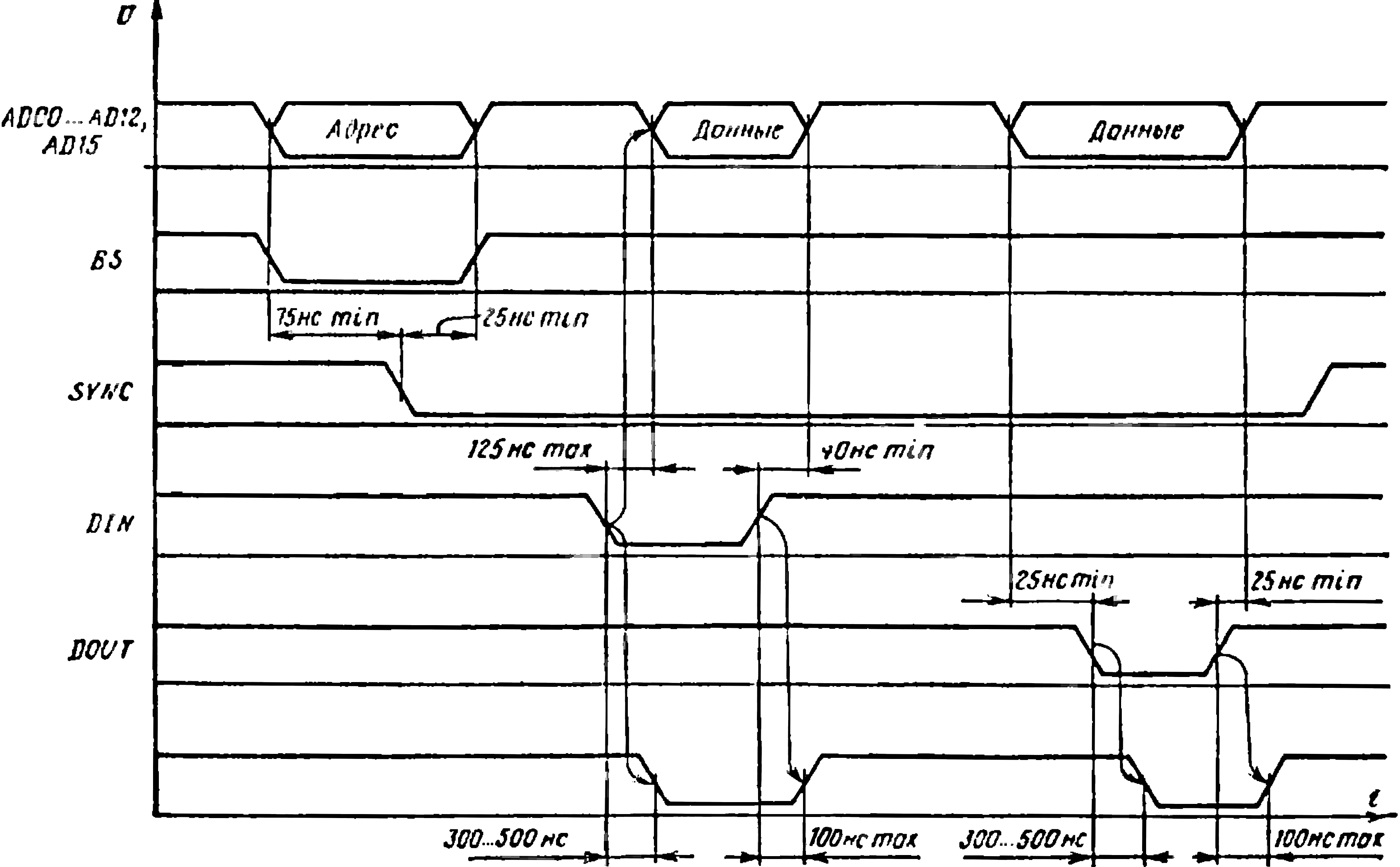

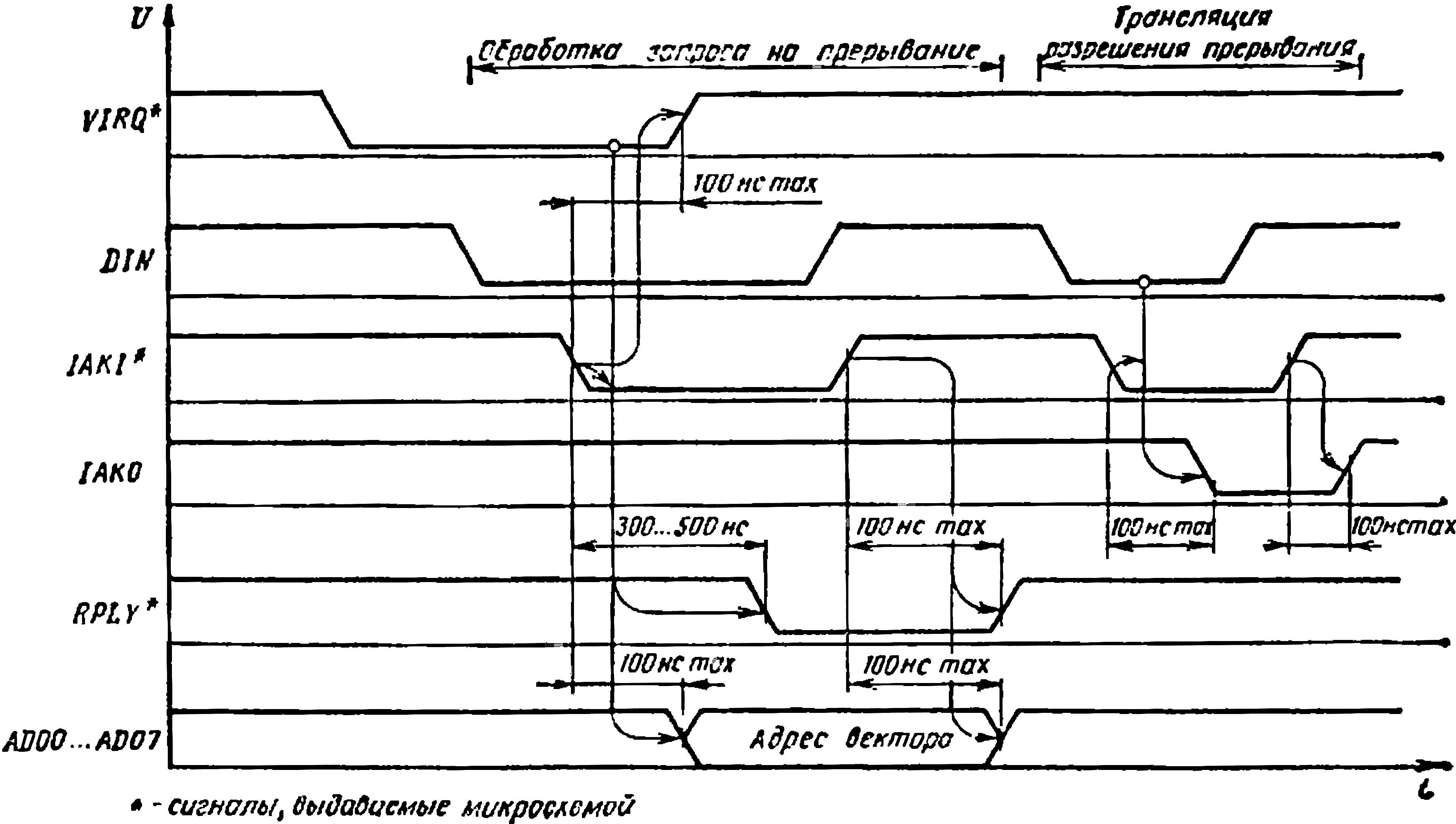

Временные диаграммы операций чтения, записи, чтения-модификации-записи и прерывания приведены на рис. 8-11 соответственно.

Рис. 8. Временная диаграмма операции чтение (ввод)

Рис. 9. Временная диаграмма операции запись (вывод)

Рис. 10. Временная диаграмма операции чтение-модификация-запись (ввод-пауза-вывод)

Рис. 11. Временная диаграмма операции прерывания

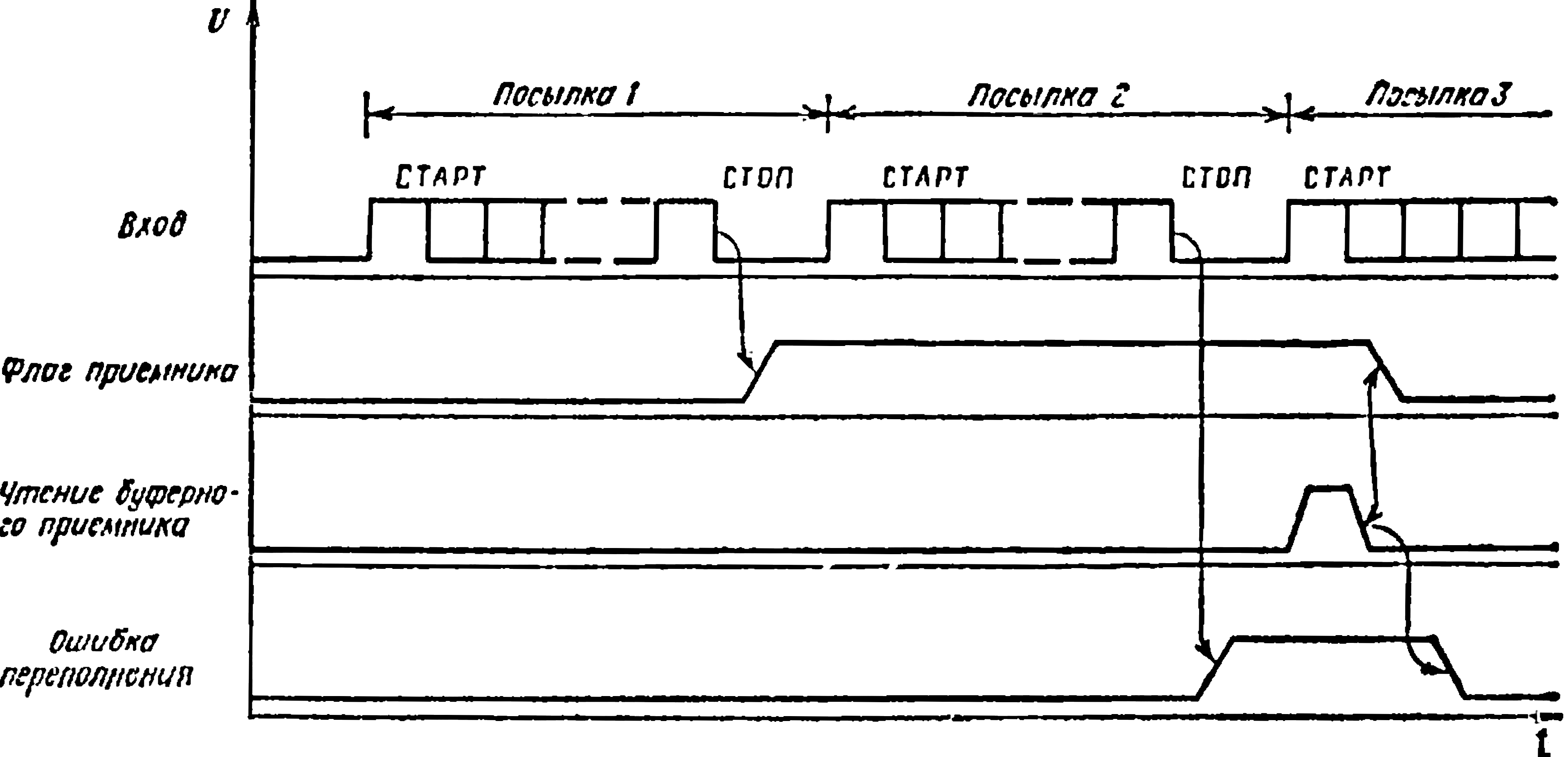

Работа приёмника

Информация в последовательном коде поступает со входа IP в сдвиговый регистр и по окончании сдвига переписывается в буферный регистр. В разряде 7 регистра состояния приёмника выставляется флаг готовности приёмника. Если в разряде 6 регистра состояния записано условие работы канала приёмника микросхемы по прерыванию, то на выходе VIRQ возникает сигнал запроса на прерывание. Запрос должен быть обработан по системной магистрали процессором, в результате чего по адресу буферного регистра должна быть прочитана посылка. По окончании чтения посылки флаг готовности приёмника в разряде 7 сбрасывается и приёмник может принимать новую посылку.

При отсутствии условия разрешения прерывания (разряд 6 регистра состояния приёмника содержит Лог. 0) требование прерывания на выходе VIRQ не возникает. Процессор должен работать с микросхемой в режиме сканирования (периодического чтения по адресу) регистра состояния приёмника и после чтения флага готовности приёмника прочитать посылку из буферного регистра приёмника.

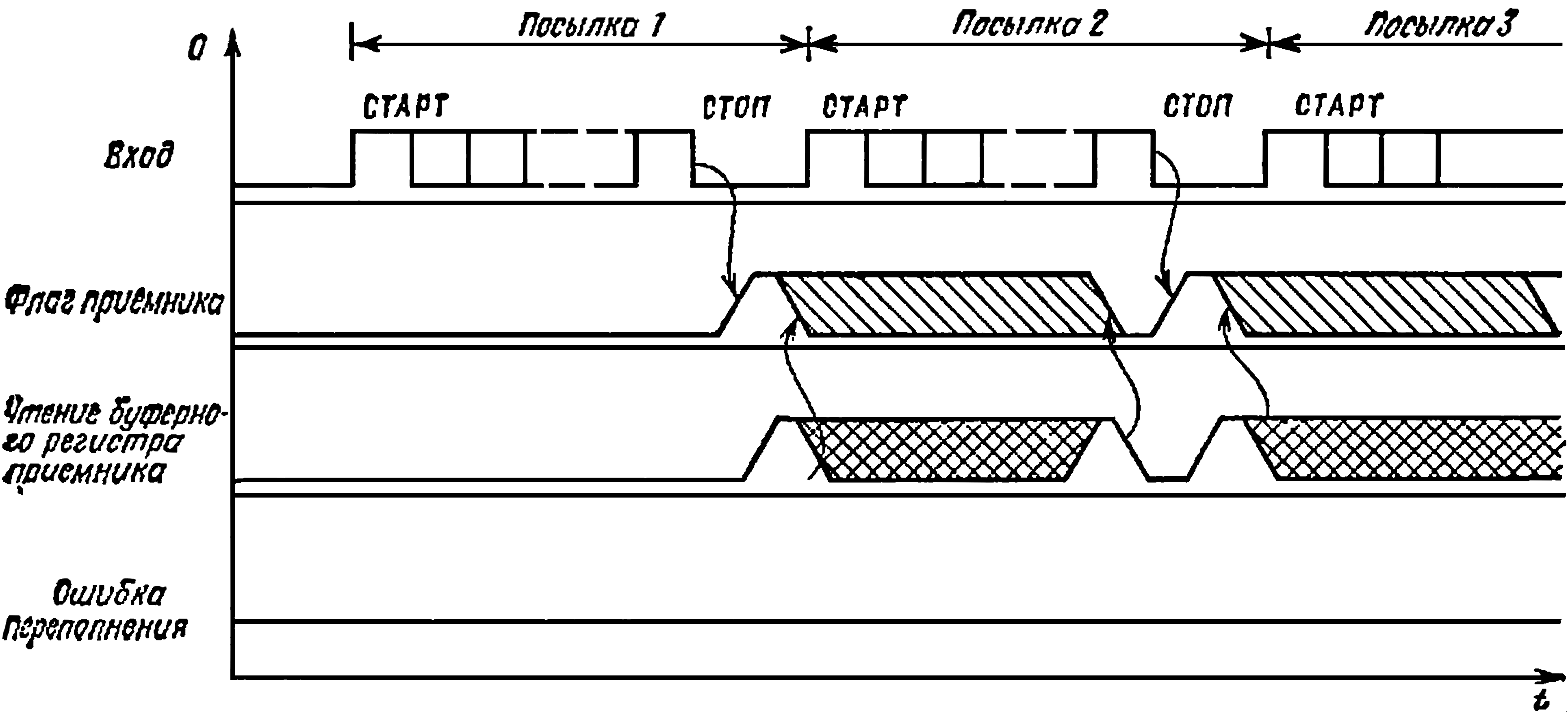

Пример приёма посылки приведён па рис. 12. Чтение флага готовности приёмника и ошибки паритета на рис. 12 не показаны. Поступившую в буферный регистр приёмника посылку можно читать не позднее поступления в сдвиговый регистр последнего информационного бита следующей посылки, иначе возникает ошибка переполнения (рис. 13). Приём посылок без возникновения ошибки переполнения приведён на рис. 14.

Работа передатчика

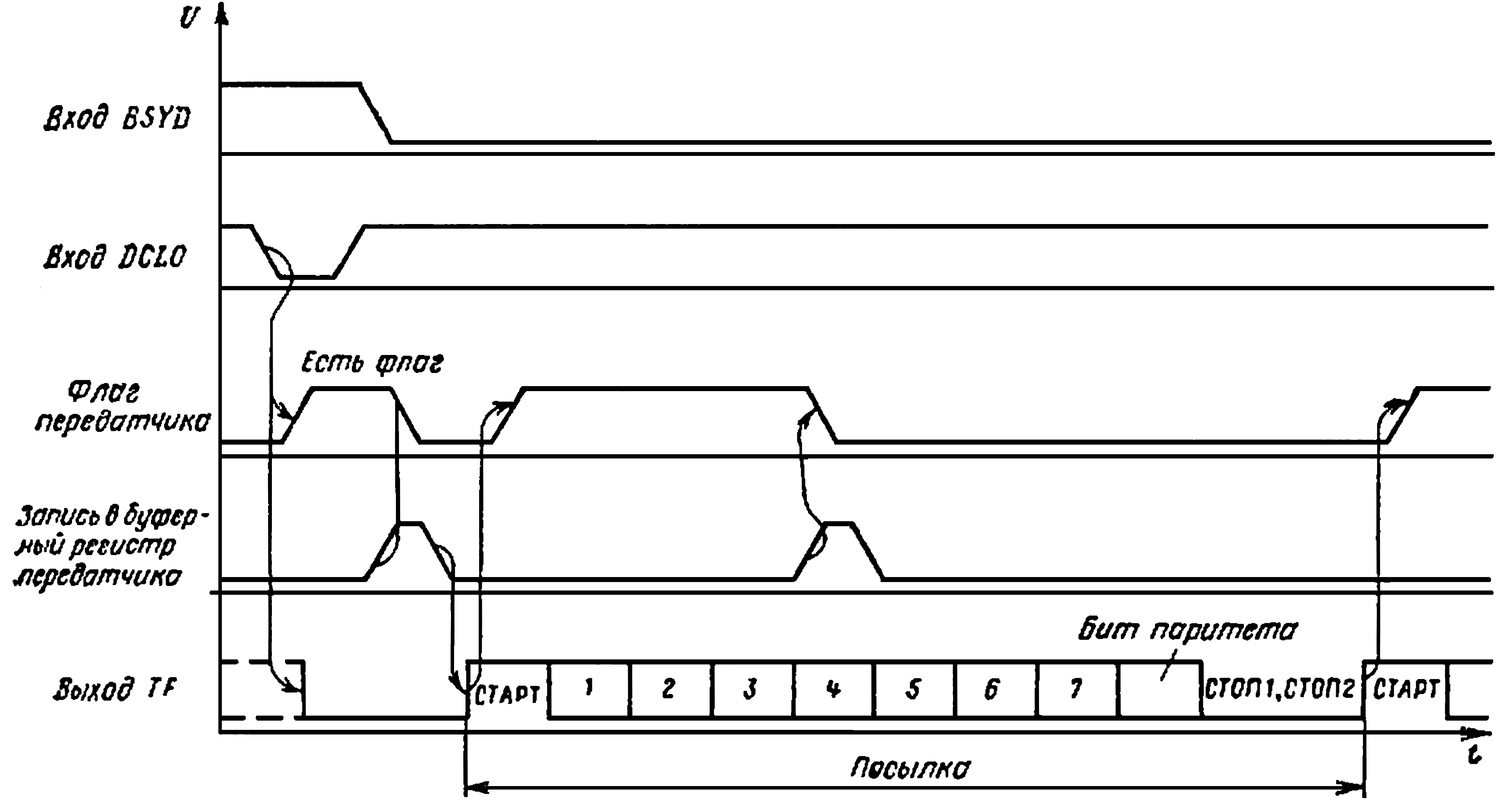

В исходном состоянии после подачи низкого уровня на вход DCLO микросхема выставляет в разряде 7 регистра состояния флаг готовности передатчика, свидетельствующий о том. что буферный регистр передатчика пуст. В разряде 6 регистра состояния может быть записано или не записано условие работы передатчика микросхемы по прерыванию. Алгоритм работы передатчика микросхемы по прерыванию или без него аналогичен описанию работы приёмника.

Информация из системной магистрали записывается по адресу буферного регистра передатчика. По окончании записи она в параллельном коде переписывается в сдвиговый регистр. При отсутствии сигнала BSYD на выходе TF через t=1/16 длительности бита появляется посылка, автоматически выдвигаемая из сдвигового регистра. С началом сдвига посылки в регистре состояния передатчика выставляется флаг готовности, свидетельствующий о том, что буферный регистр передатчика пуст и в него можно записывать новую информацию.

Если запись новой информации произведена во время выдачи посылки на линию, то новая посылка выйдет сразу же после окончания текущей посылки, т.е. после бита СТОП на выходе TF появляется бит СТАРТ новой посылки.

Рис 12. Временная диаграмма приёма седьмой байтовой посылки

Рис. 13 Временная диаграмма возникновения ошибки переполнения при приёме посылок

Рис. 14. Приём посылок без возникновения ошибки переполнения

Рис. 15. Временная диаграмма выдачи 7-битовой посылки с формированием бита паритета и двумя СТОП-битами

Пример выдачи посылки показан на рис. 15. Сигнал занятости канала BSYD влияет на выход TF и схему синхронизации канала передатчика. Если на входе BSYD низкий уровень, то канал передатчика работает, как описано выше. Если на вход BSYD подать высокий уровень, то на выходе TF устанавливается низкий уровень (СТОП) независимо от того, выходит посылка или нет, и тормозится выдача посылки. Если во время действия высокого уровня на входе BSYD происходит запись данных в буферный регистр передатчика, то эти данные не переписываются в сдвиговый регистр передатчика. После снятия высокого уровня со входа BSYD записанная в буферный регистр посылка переписывается в сдвиговый регистр и на выходе TF через t=1/16 длительности бита появляется бит СТАРТ данной посылки и возникает новый флаг готовности передатчика.

Г. Г. Глушкова

Телефон 208-73-23, Москва