УДК 681.3.01 : 51

ИНТЕРФЕЙСНЫЕ БИС МИКРОПРОЦЕССОРНОГО КОМПЛЕКТА К1801: МИКРОСХЕМА К1801ВП1-034

(Продолжение цикла. Начало в № 4, 5, 1988)

Микросхема К1801ВП1-034 представляет собой многофункциональное устройство, работающее в следующих режимах:

- передачи информации;

- выдачи вектора прерывания и как компаратор адреса;

- буферного регистра данных.

Используется БИС К1801ВП1-034 как самостоятельное устройство и совместно с микросхемой К1801ВП1-033[*] для организации интерфейсов байтового параллельного ввода и 16-разрядного программируемого параллельного ввода-вывода.

Режим передачи информации

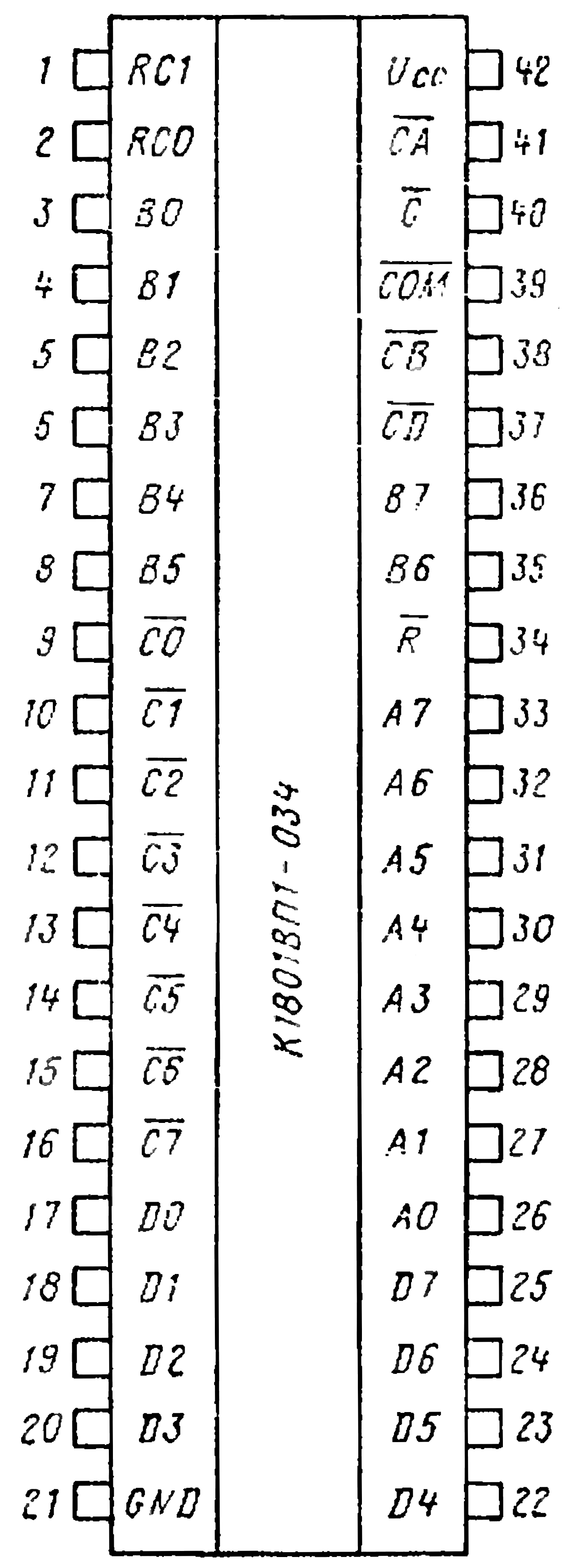

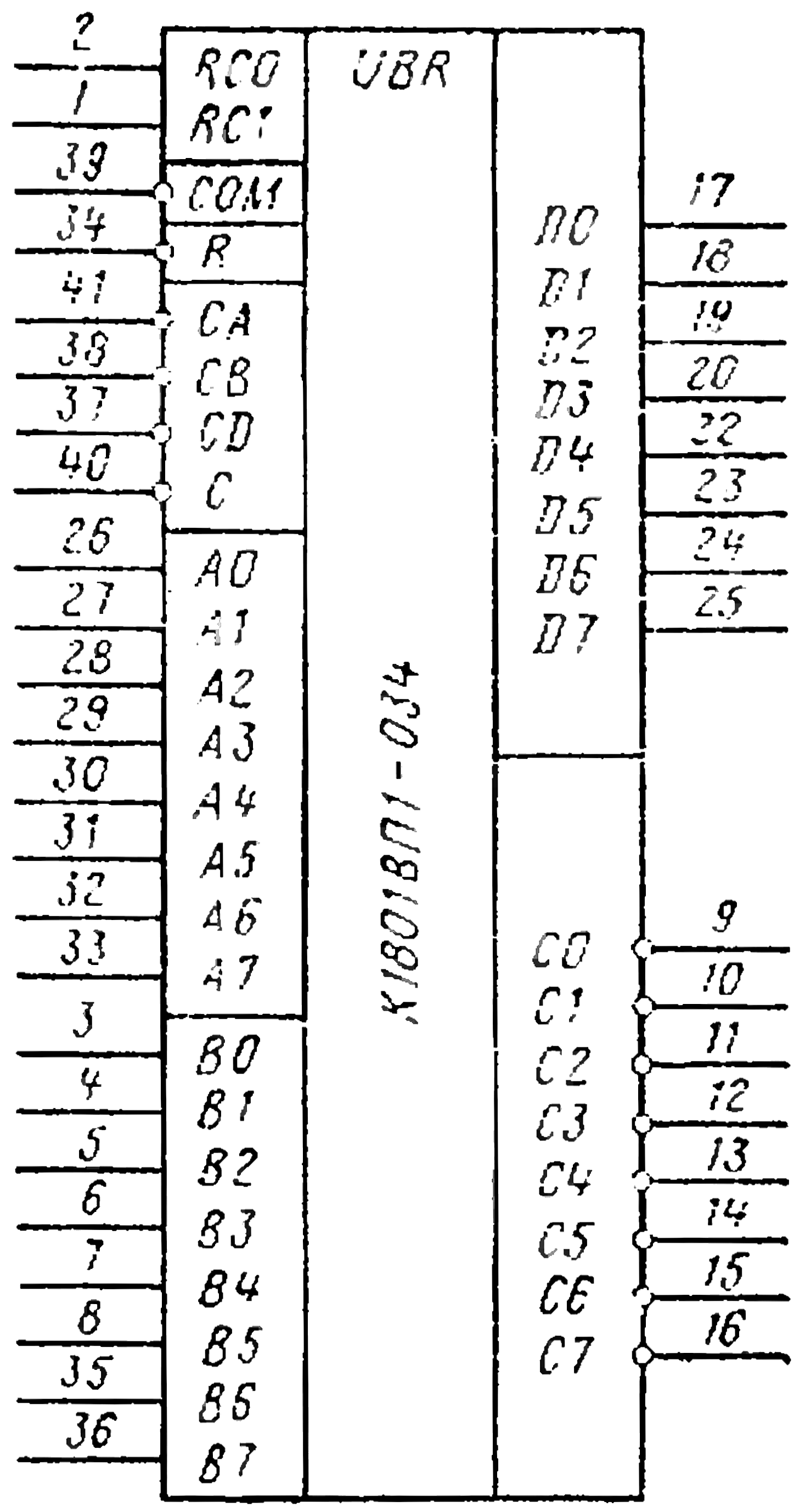

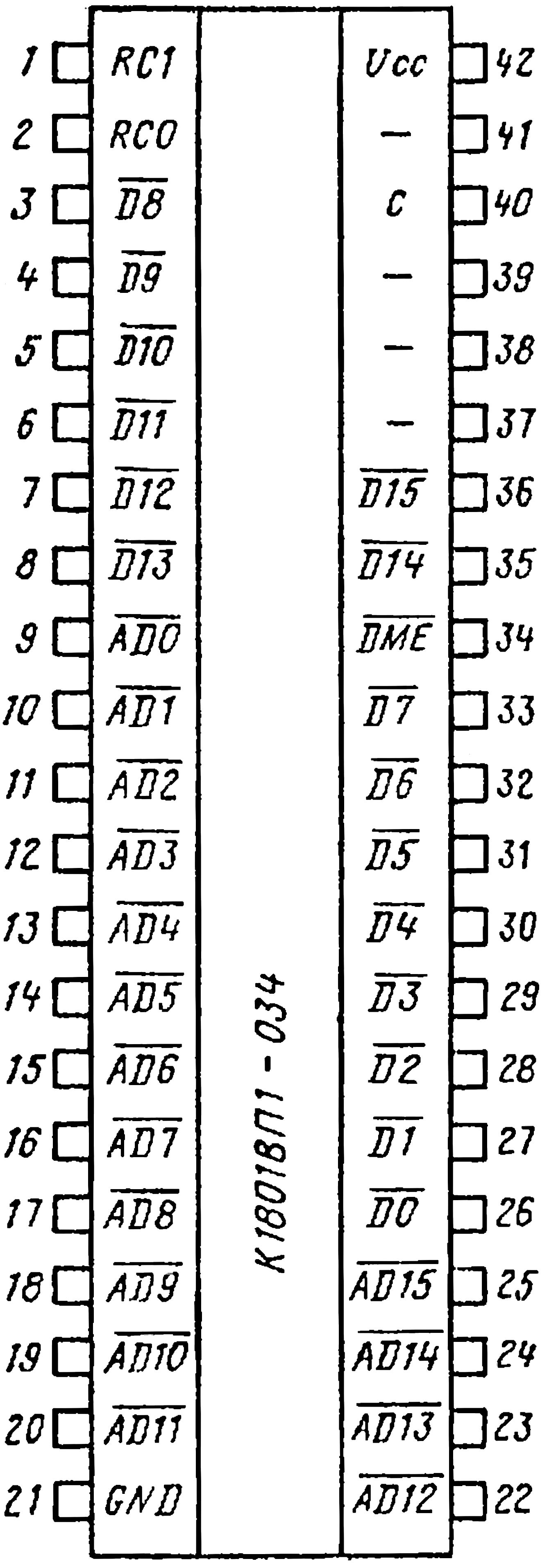

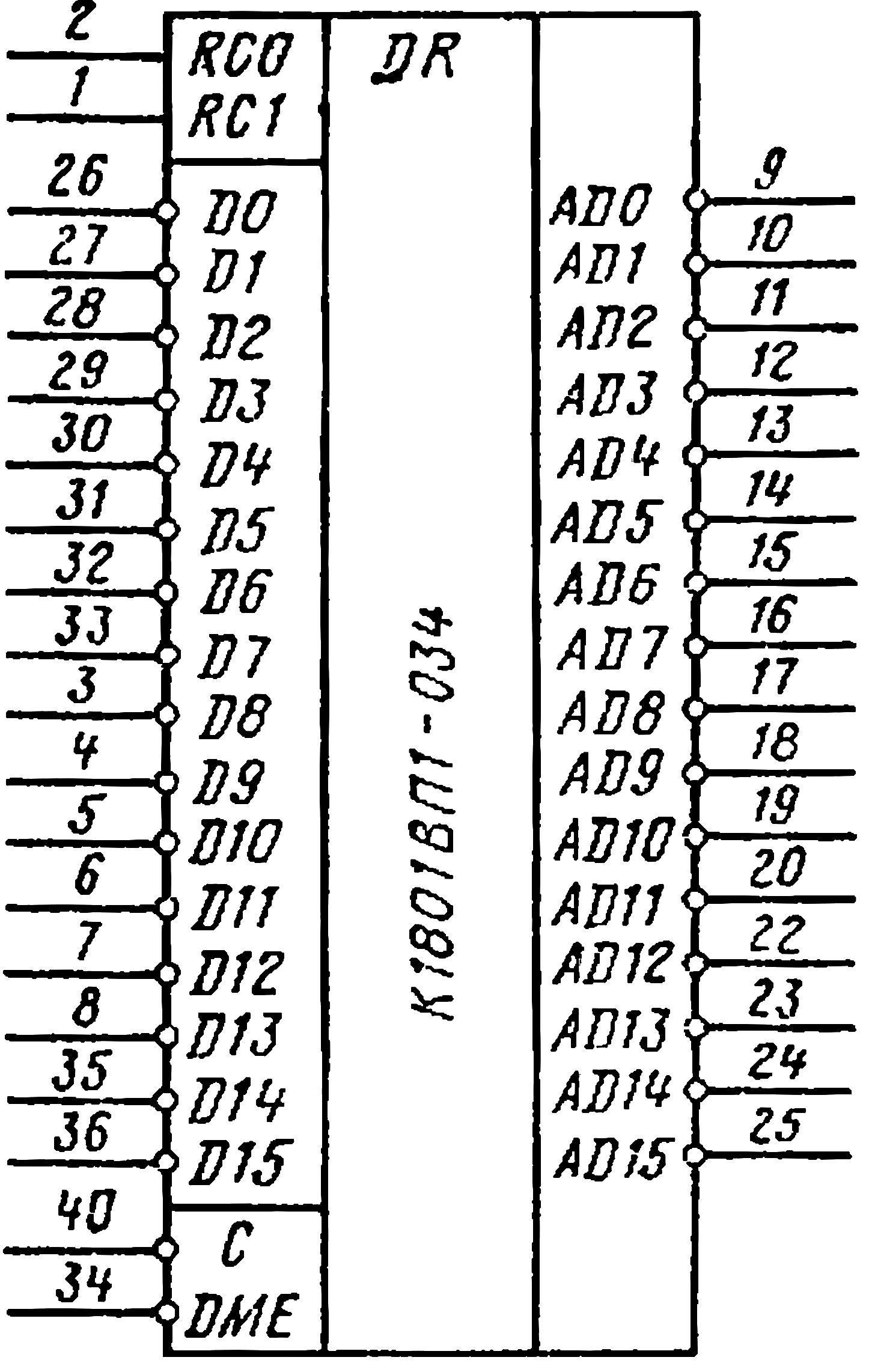

Условное графическое обозначение микросхемы К1801ВП1-034 в этом режиме приведено на рис. 1, назначение выводов показано в табл. 1, электрическая структурная схема представлена на рис. 2.

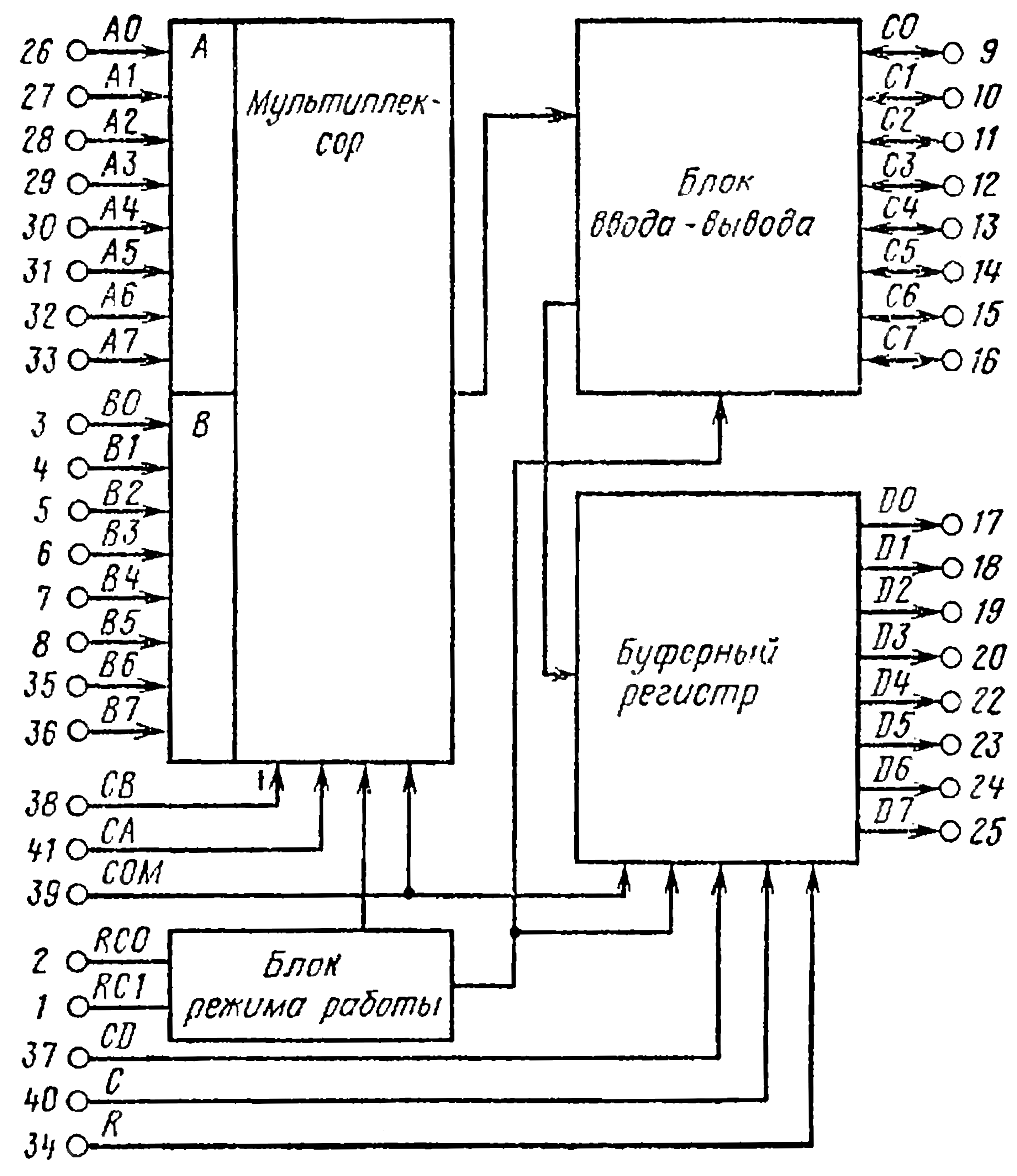

В режим устройства передачи информации (УПИ) микросхема устанавливается подачей на вывод RC0 высокого, а на выход RC1 - низкого уровней напряжения. С помощью управляющих сигналов CA и CB входная информация A0...A7 и B0...B7 соответственно передаётся на двунаправленные выводы C0...C7 в зависимости от сигнала COM в прямом или инверсном, виде (рис. 3). Сигналом C информация с выводов C0...C7 записывается в буферный регистр и с помощью сигнала CD выдаётся на выводы D0...D7 в зависимости от сигнала COM в прямом или инверсном виде. Сигнал R обнуляет буферный регистр.

|

|

Рис. 1. Условное графическое обозначение микросхемы К1801ВП1-034 в режиме передачи данных по порядку расположения (а) и функциональному назначению (б) выводов

|

|

Вывод |

Обозначение |

Тип вывода |

Наименование вывода |

|---|---|---|---|

|

1 |

RC1 |

Вход |

Выбор режима 1 |

|

2 |

RC0 |

Вход |

Выбор режима 0 |

|

3...8 |

B0... B5 |

Вход |

Данные B0 ... B5 |

|

9...16 |

C0... C7 |

Вход-выход |

Данные каналов AD0 ... AD7 |

|

17...20 |

D0...D3 |

Выход |

Данные D0 ... D3 |

|

21 |

GND |

- |

Общий |

|

22...25 |

D4 ... D7 |

Выход |

Данные D4 ... D7 |

|

26...33 |

A0 ... A7 |

Вход |

Данные A0 ... А7 |

|

34 |

R |

Вход |

Сброс данных |

|

35 |

B6 |

Вход |

Данные В6 |

|

36 |

B7 |

Вход |

Данные В7 |

|

37 |

CD |

Вход |

Разрешение выдачи данных D |

|

38 |

CB |

Вход |

Разрешение выдачи данных В |

|

39 |

COM |

Вход |

Инвертирование данных |

|

40 |

C |

Вход |

Запись данных |

|

41 |

CA |

Вход |

Разрешение выдачи данных А |

|

42 |

Ucc |

- |

Напряжение источника питания |

Рис. 2. Электрическая структурная схема устройства передачи информации

Рис. 3. Временная диаграмма работы устройства передачи информации

Режим выдачи вектора прерывания и компаратора адреса.

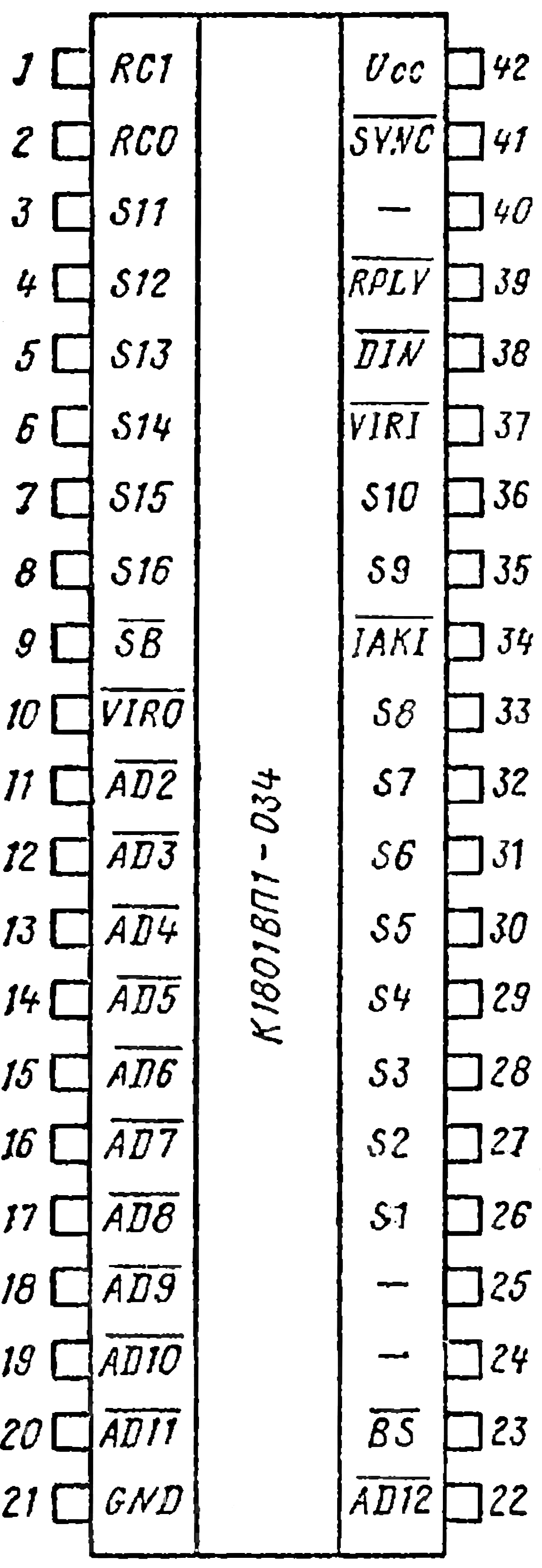

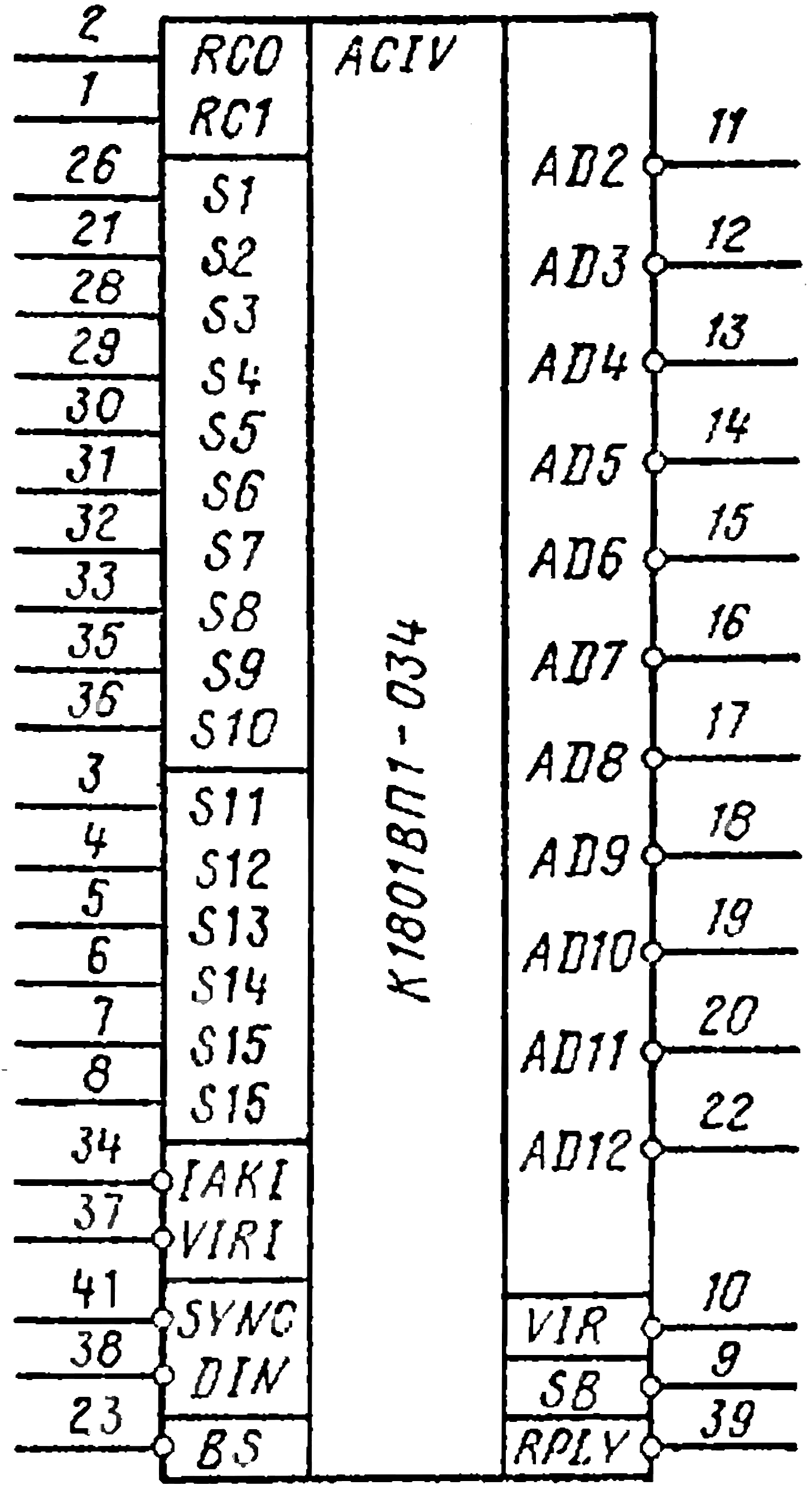

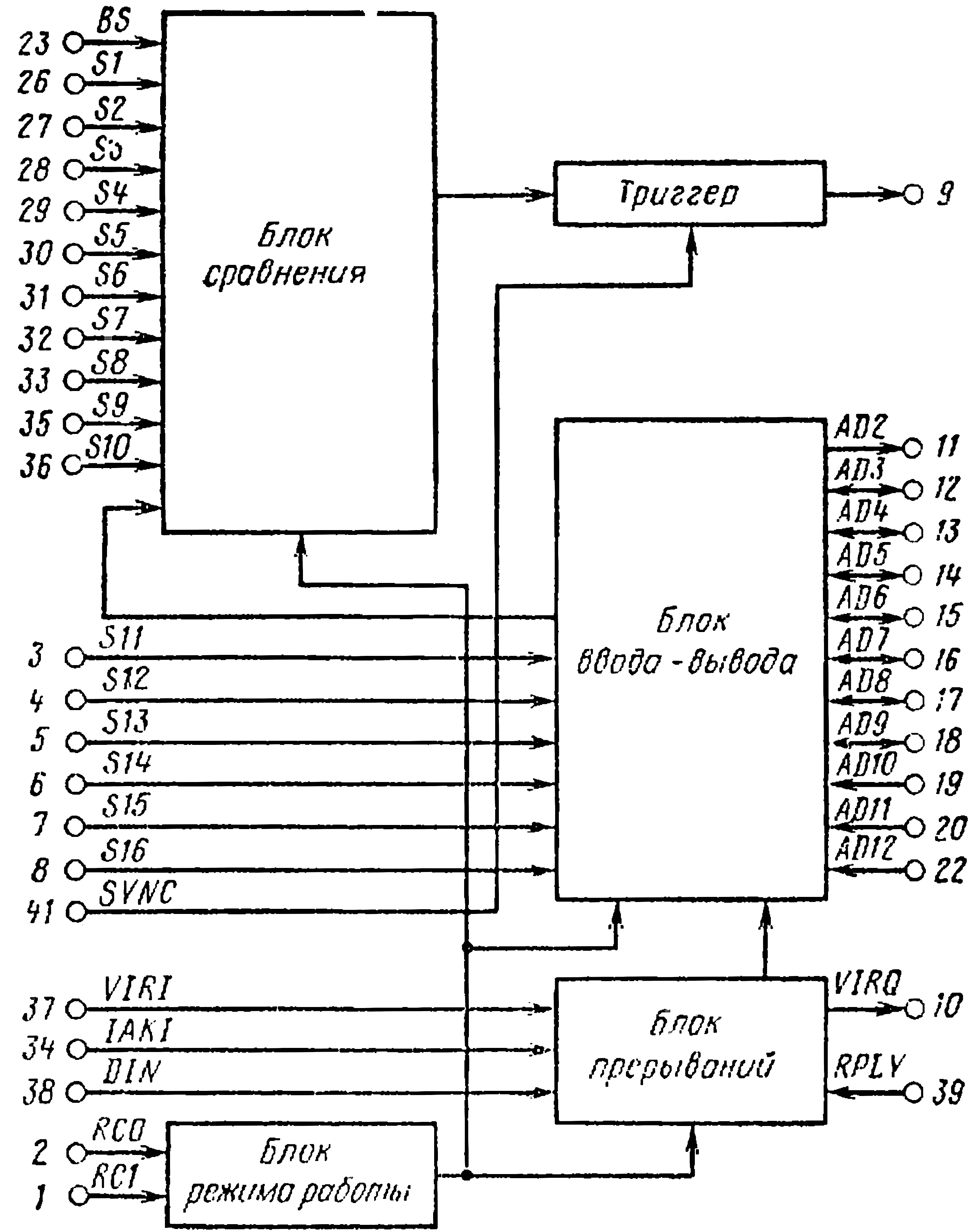

Условное графическое обозначение микросхемы в этом режиме дано на рис. 4, назначение выводов доказано в табл. 2, электрическая структурная схема приведена на рис. 5.

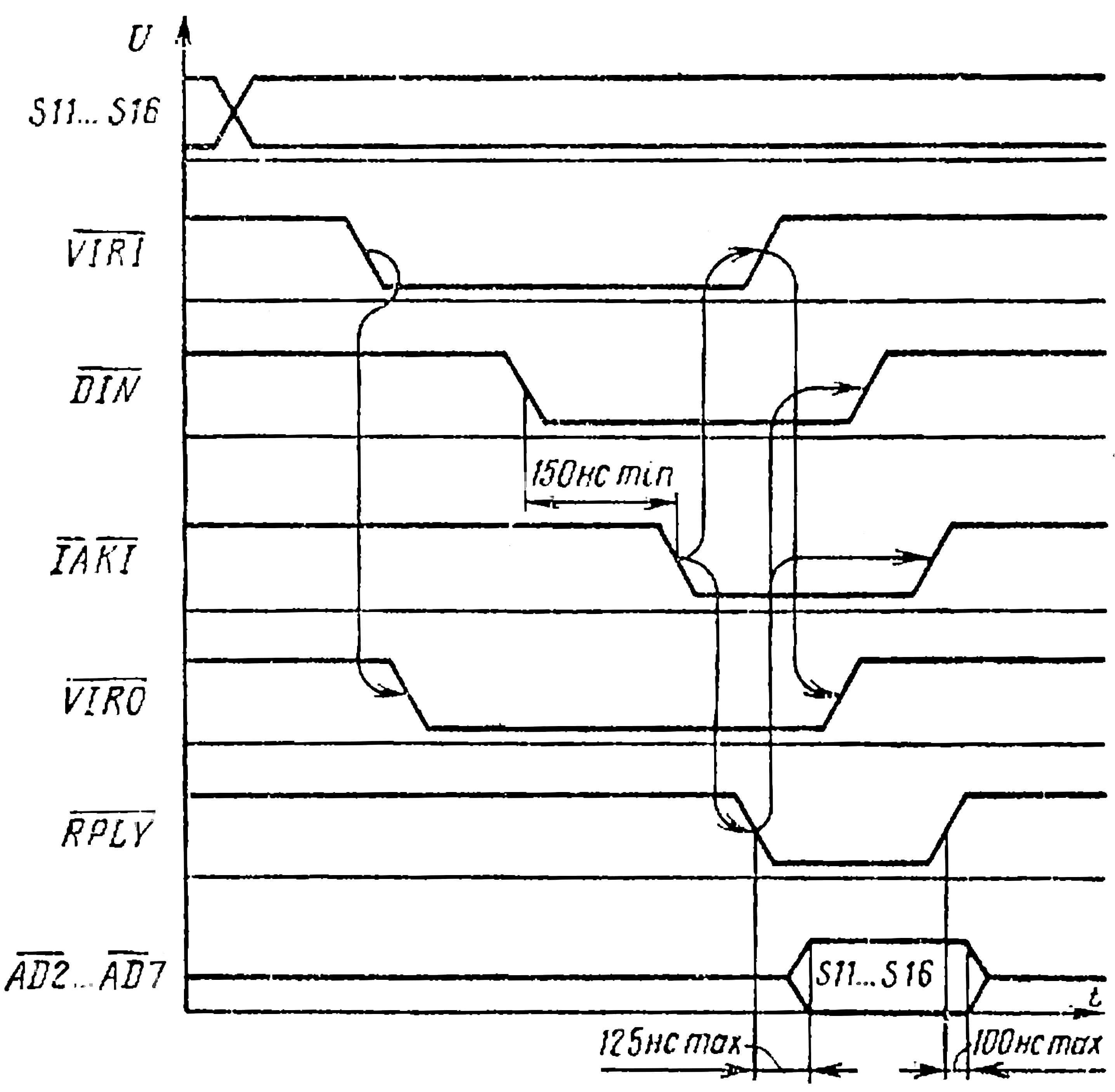

Микросхема устанавливается в режим выдачи вектора прерывания с момента подачи на выводы RC0 и RC1 напряжения высокого уровня. Старшие шесть разрядов требуемого адреса вектора прерывания формируются на выводах S11...S16. Временная диаграмма выполнения стандартной процедуры прерывания представлена на рис. 6.

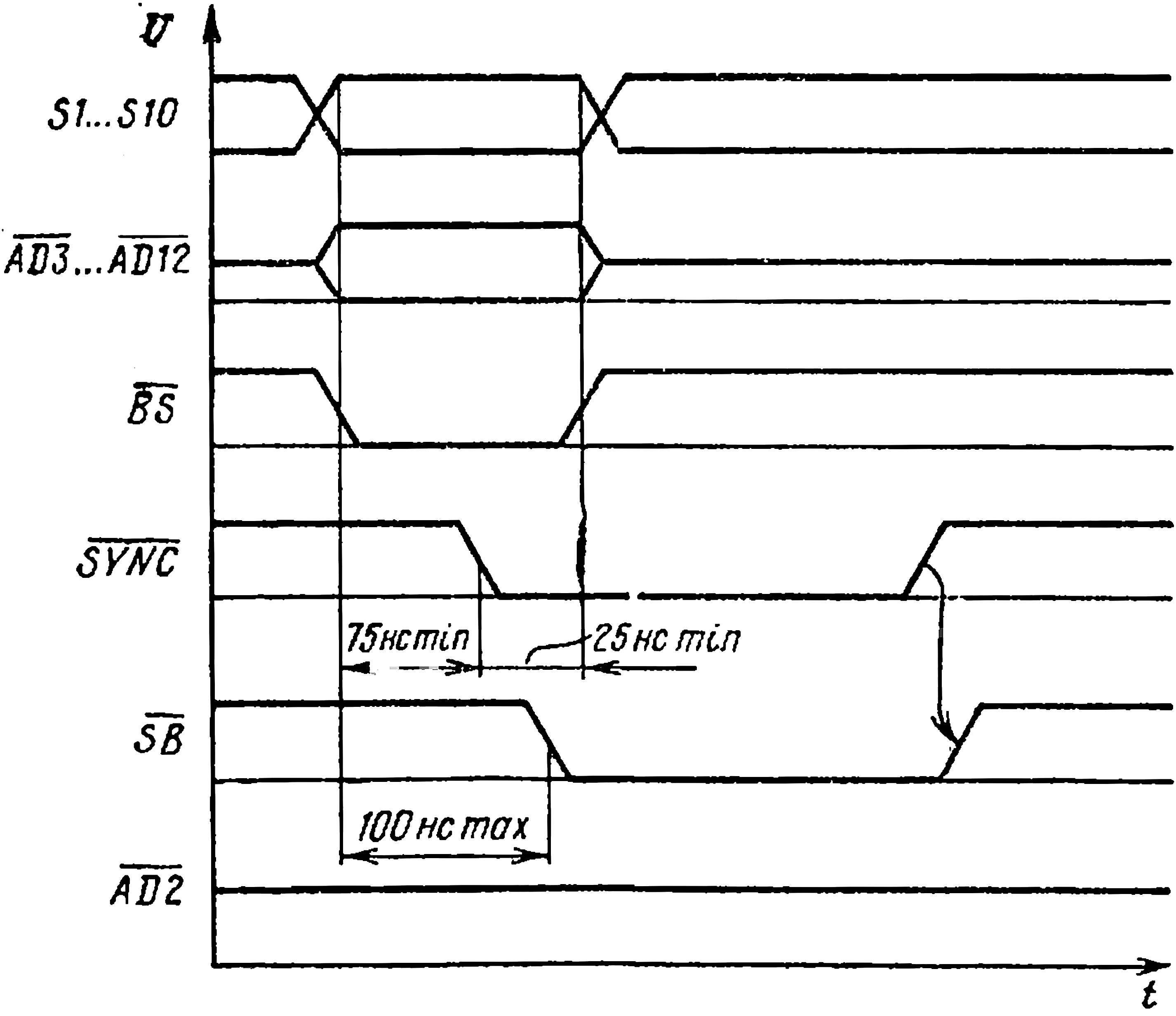

Адрес, необходимый для сравнения, снимается с выводов S1...S10. Состояния S1...S10 и AD3...AD12 сравниваются при наличии сигнала BS. В результате сравнения вырабатывается сигнал SB, запоминаемый в триггере на всё время действия сигнала SYNC. Временная диаграмма работы компаратора адреса приведена на рис. 7.

|

|

Рис. 4. Условное графическое обозначение микросхемы К1801ВП1-034 в режиме выдачи вектора прерывания я компаратора адреса по порядку расположения (а) и функциональному назначению (б) выводов

|

|

Вывод |

Обозначение |

Тип вывода |

Наименование вывода |

|---|---|---|---|

|

1 |

RC1 |

Вход |

Выбор режима 1 |

|

2 |

RC0 |

Вход |

Выбор режима 0 |

|

3...8 |

S11 ... S16 |

Вход |

Зашивка вектора прерывания 2 ... 7 |

|

9 |

SB |

Выход |

Устройство выбрано |

|

10 |

VIRO |

Выход |

Запрос на прерывание |

|

11...20 |

AD2 ... AD11 |

Вход-выход |

Разряды адреса-данных |

|

21 |

GND |

- |

Общий |

|

22 |

AD12 |

Вход-выход |

12-й разряд адреса-данных |

|

23 |

BS |

Вход |

Внешнее устройство |

|

24, 25 |

|

- |

Не используются |

|

26...33 |

S1 ... S8 |

Вход |

Зашивка адреса 3 ... 10 |

|

34 |

IAKI |

Вход |

Разрешение прерывания |

|

35 |

S9 |

Вход |

Зашивка адреса 11 |

|

36 |

S10 |

Вход |

Зашивка адреса 12 |

|

37 |

VIRI |

Вход |

Запрос прерывания |

|

38 |

DIN |

Вход |

Чтение данных |

|

39 |

RPLY |

Выход |

Ответ |

|

40 |

- |

- |

Не используется |

|

41 |

SYNC |

Вход |

Обмен |

|

42 |

Ucc |

- |

Напряжение источника питания |

Рис. 5. Электрическая структурная схема устройства выдачи вектора прерывания и компаратора адреса

Рис. 6. Временная диаграмма работы устройства выдачи вектора прерывания

Рис. 7. Временная диаграмма работы компаратора адреса

Режим буферного регистра

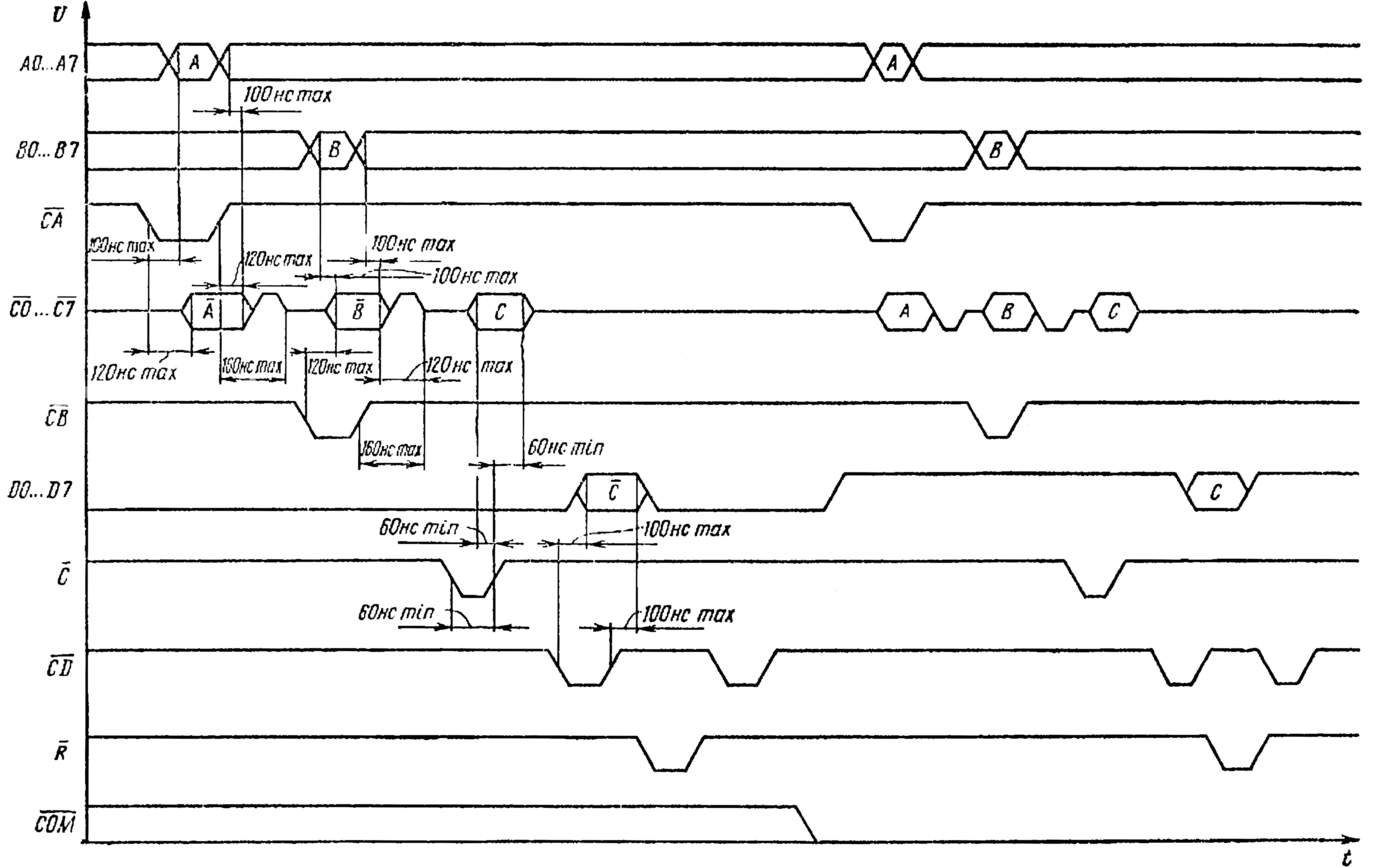

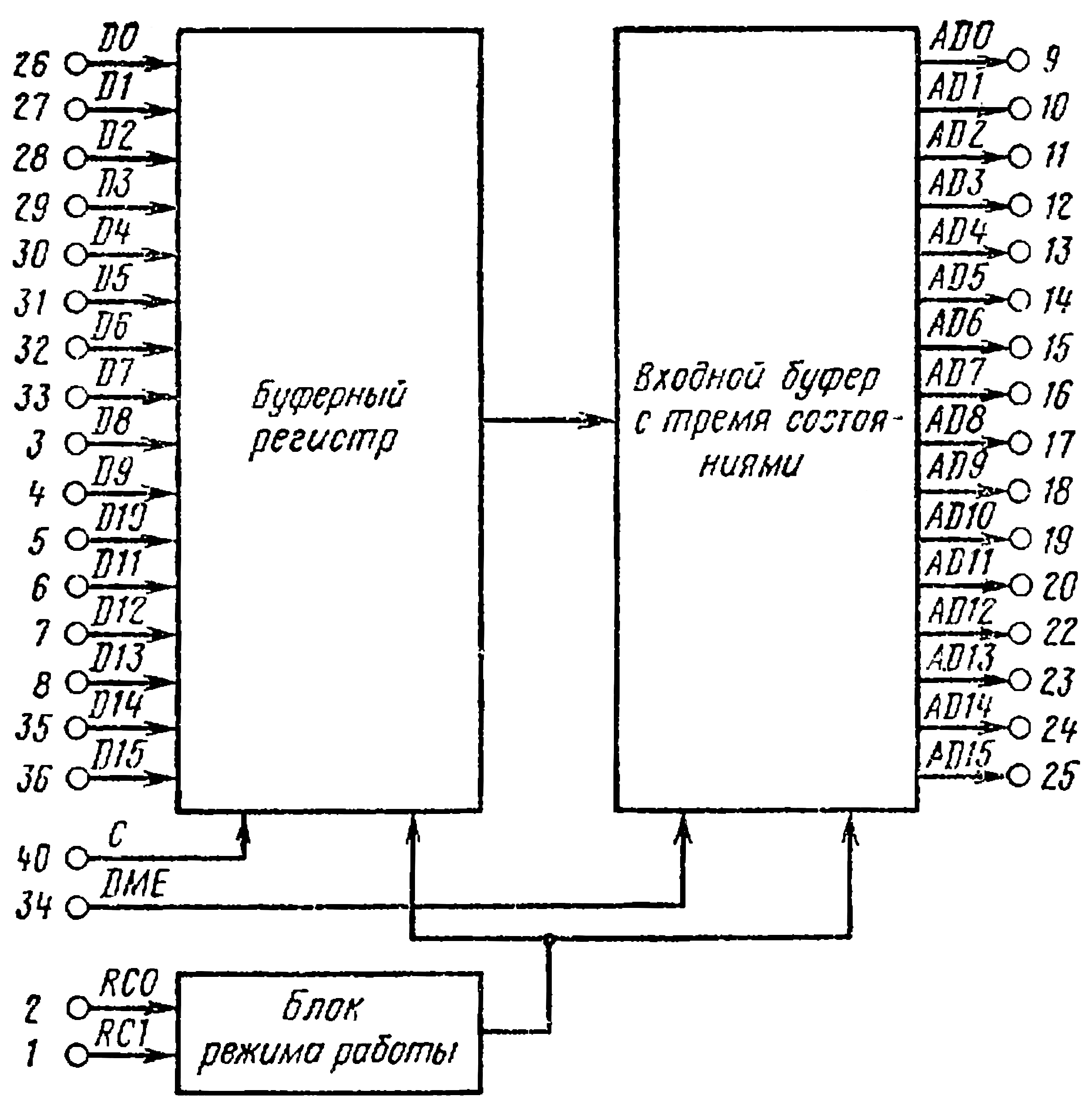

Этот режим устанавливается при напряжении низкого уровня на выводе RC0 и высокого уровня на RC1. Условное графическое обозначение БИС К1801ВП1-034 в указанном режиме приведено на рис. 8, назначение выводов показано в табл. 3, электрическая структурная схема дана на рис. 9.

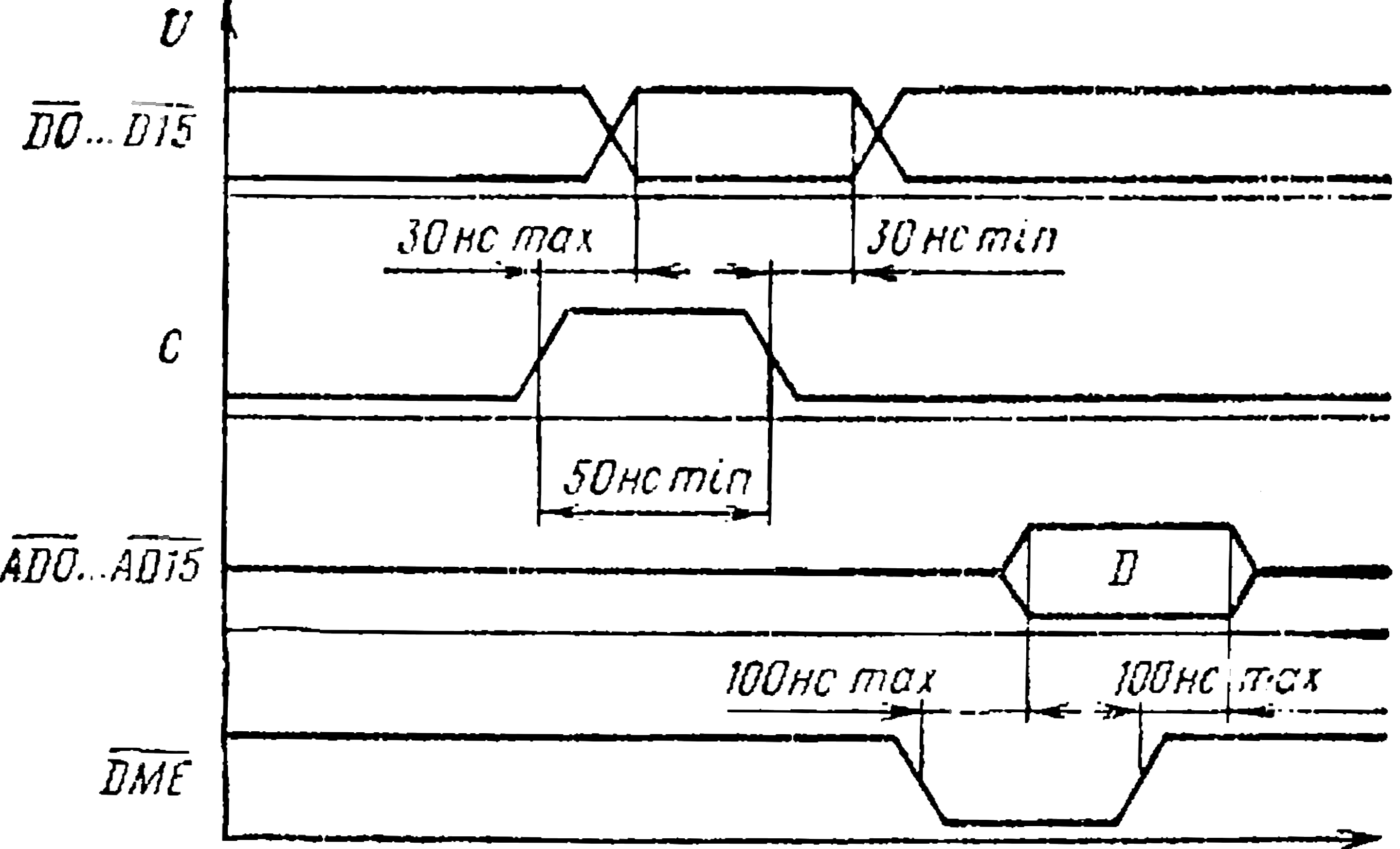

Входная информация с выводов D0...D15 сигналом С записывается в 16-разрядный буферный регистр. Сигнал DME разрешает выдачу информации с буферного регистра на выводы AD0...AD15, которые при высоком уровне этого сигнала находятся в отключённом состоянии (рис. 10).

|

|

Рис. 8. Условное графическое обозначение микросхемы К1801ВП1-034 в буферном режиме по порядку расположения (а) и функциональному назначению (б) выводов |

|

Вывод |

Обозначение |

Тип вывода |

Наименование вывода |

|---|---|---|---|

|

1 |

RC1 |

Вход |

Выбор режима 1 |

|

2 |

RC0 |

Вход |

Выбор режима 0 |

|

3...8 |

D8...D13 |

Вход |

Данные D8 ... D13 |

|

9...20 |

AD0...AD11 |

Выход |

Данные канала AD0 ... AD11 |

|

21 |

GND |

- |

Общий |

|

22...25 |

AD12...AD15 |

Выход |

Данные канала AD12 ... AD15 |

|

26...33 |

D0...D7 |

Вход |

Данные D0 ... D7 |

|

34 |

DME |

Вход |

Разрешение выдачи данных |

|

35 |

D14 |

Вход |

Данные D14 |

|

36 |

D15 |

Вход |

Данные D15 |

|

37...39,41 |

- |

- |

Не используется |

|

40 |

C |

Вход |

Запись данных |

|

42 |

Ucc |

- |

Напряжение источника питания |

Рис. 9. Электрическая структурная схема буферного регистра данных

Рис. 10. Временная диаграмма режима буферного регистра данных

Г.Г. Глушкова, телефон: 208-73-23, Москва

[*] Интерфейсные БИС микропроцессорного комплекта К1801: микросхема К1801ВП1-033 // Микропроцессорные средства и системы, - 1988, - № 5, - С. 87.