УДК 681.3.01 : 51

ИНТЕРФЕЙСНЫЕ БИС МИКРОПРОЦЕССОРНОГО КОМПЛЕКТА К1801: МИКРОСХЕМА К1801ВП1-033

(Продолжение цикла. Начало в № 4, 1988)

Микросхема К1801ВП1-033 является многофункциональным устройством параллельного интерфейса и может работать в режимах:

- интерфейса накопителя на гибких магнитных дисках;

- контроллера интерфейса параллельного ввода-вывода;

- контроллера байтового параллельного интерфейса (ИРПР).

Микросхема предназначена для использования совместно с микросхемой К1801ВП1-034 для организации интерфейсного устройства 16-разрядного программируемого параллельного ввода-вывода и байтового параллельного ввода-вывода, а также в качестве самостоятельного интерфейсного устройства накопителя на гибких магнитных дисках.

Режим интерфейса накопителя на гибких магнитных дисках.

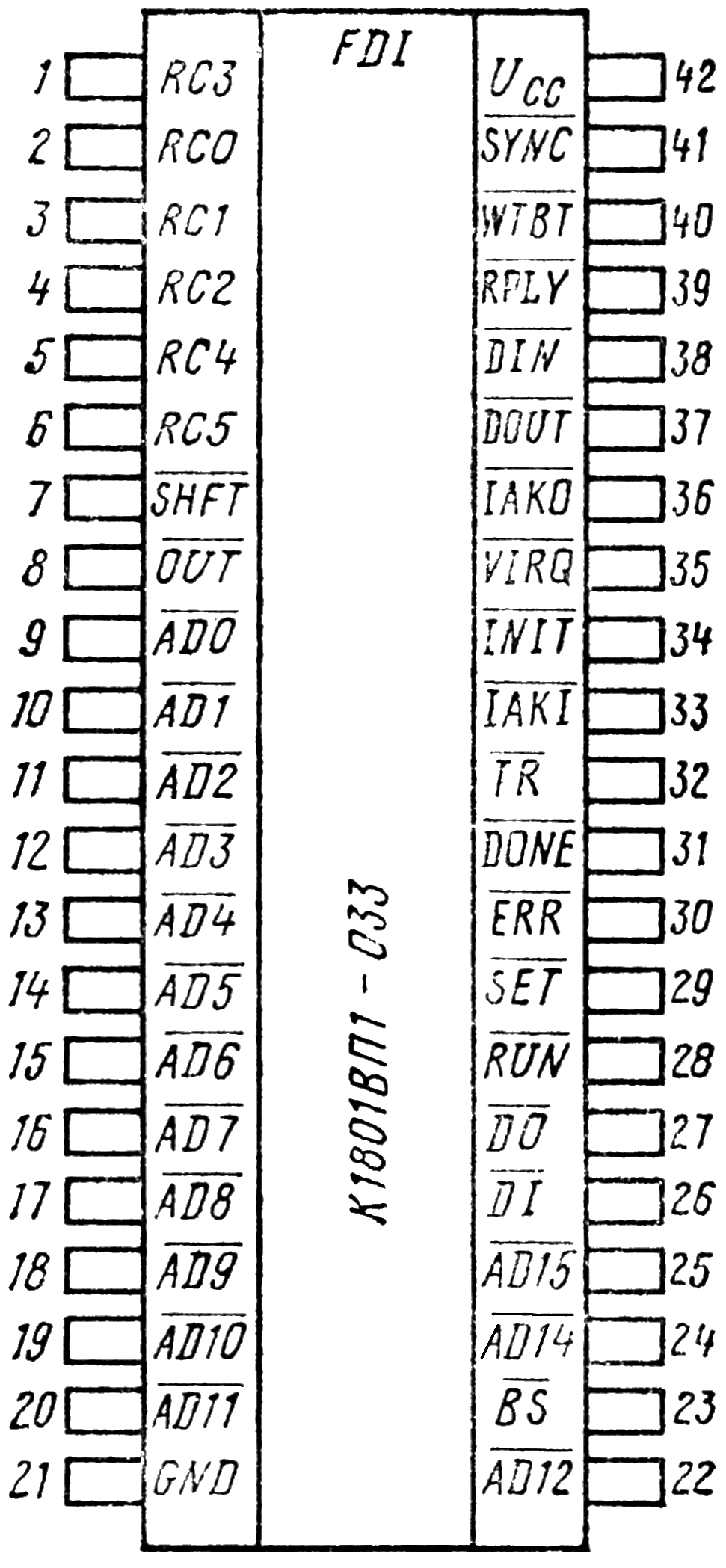

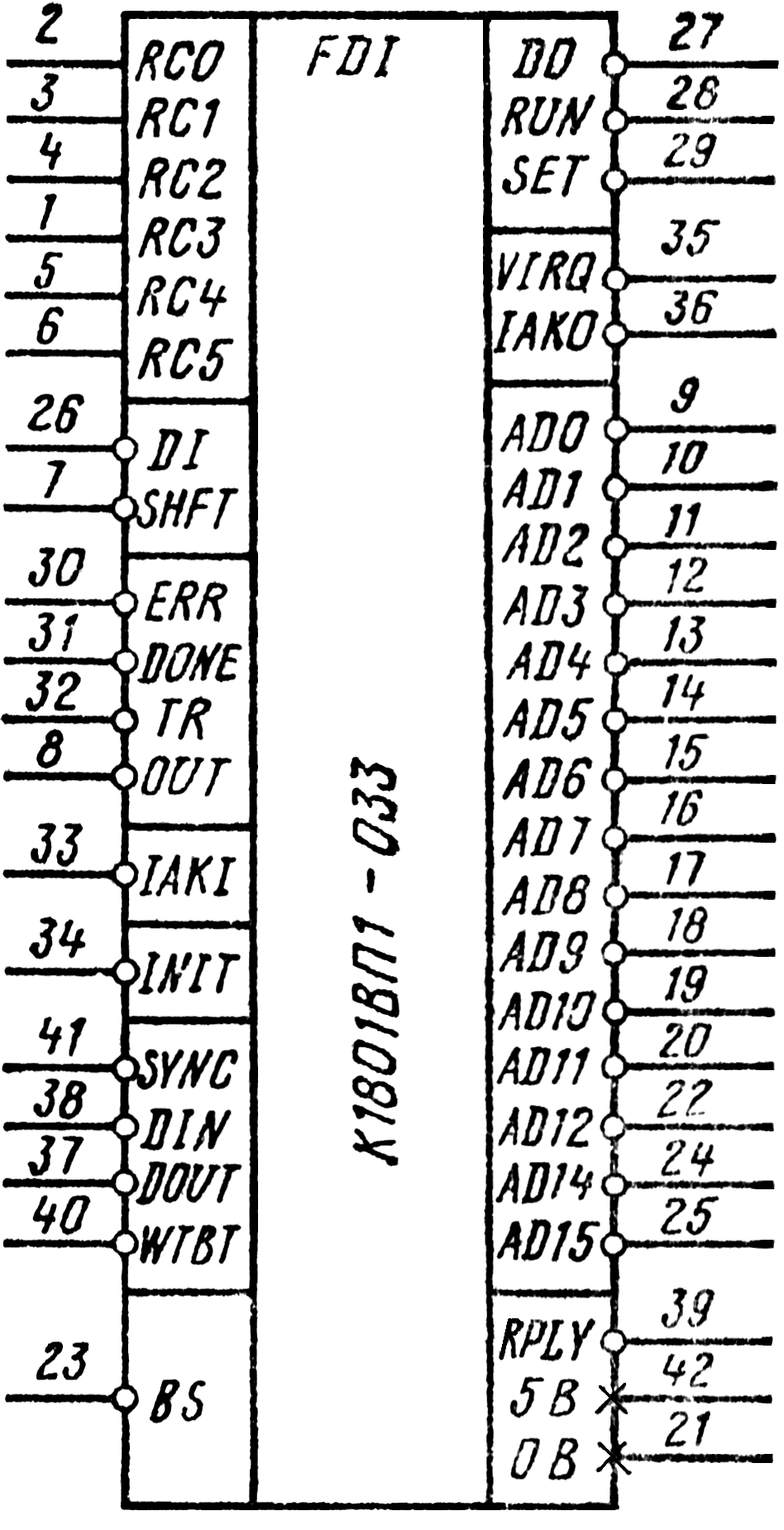

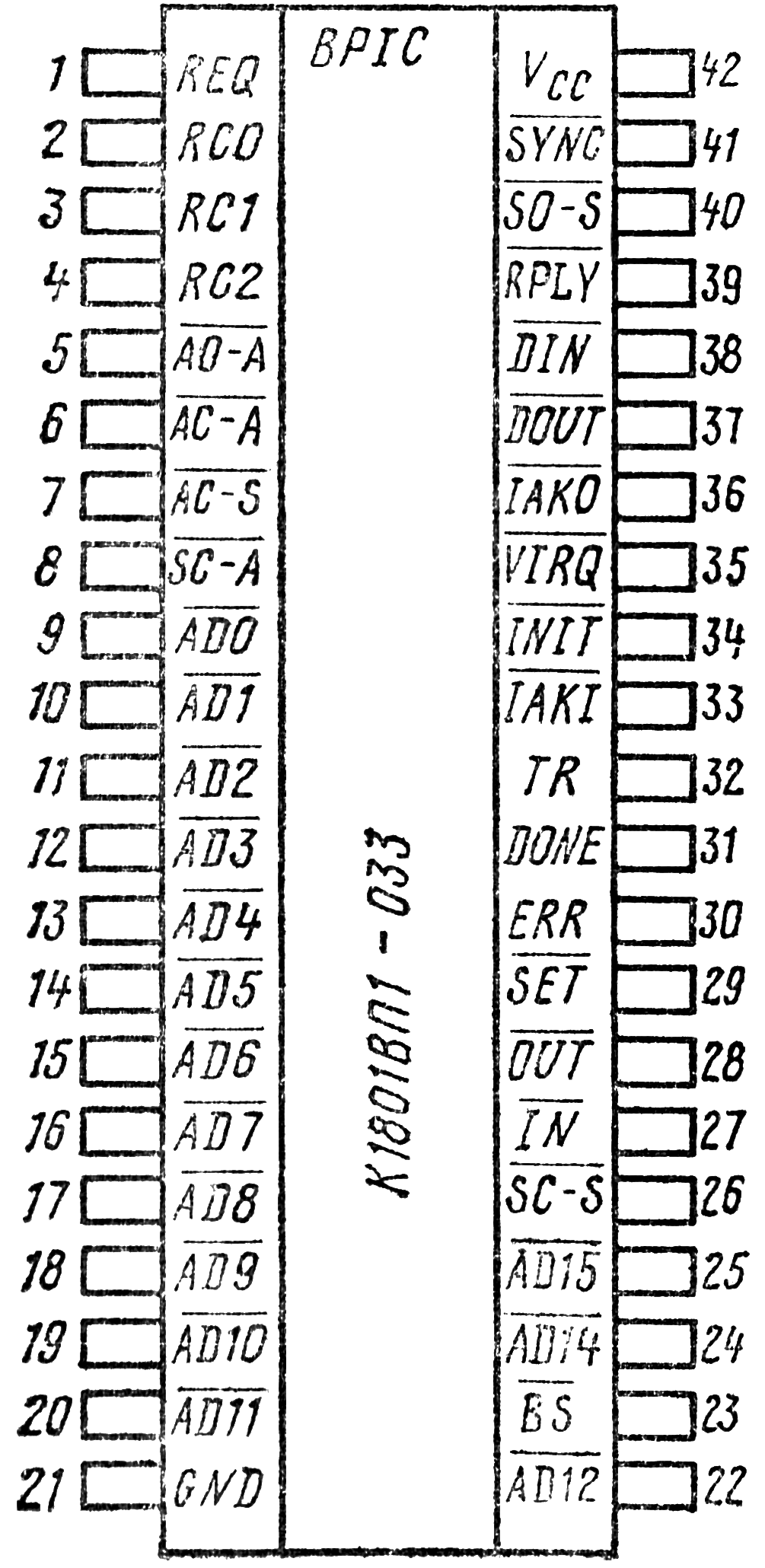

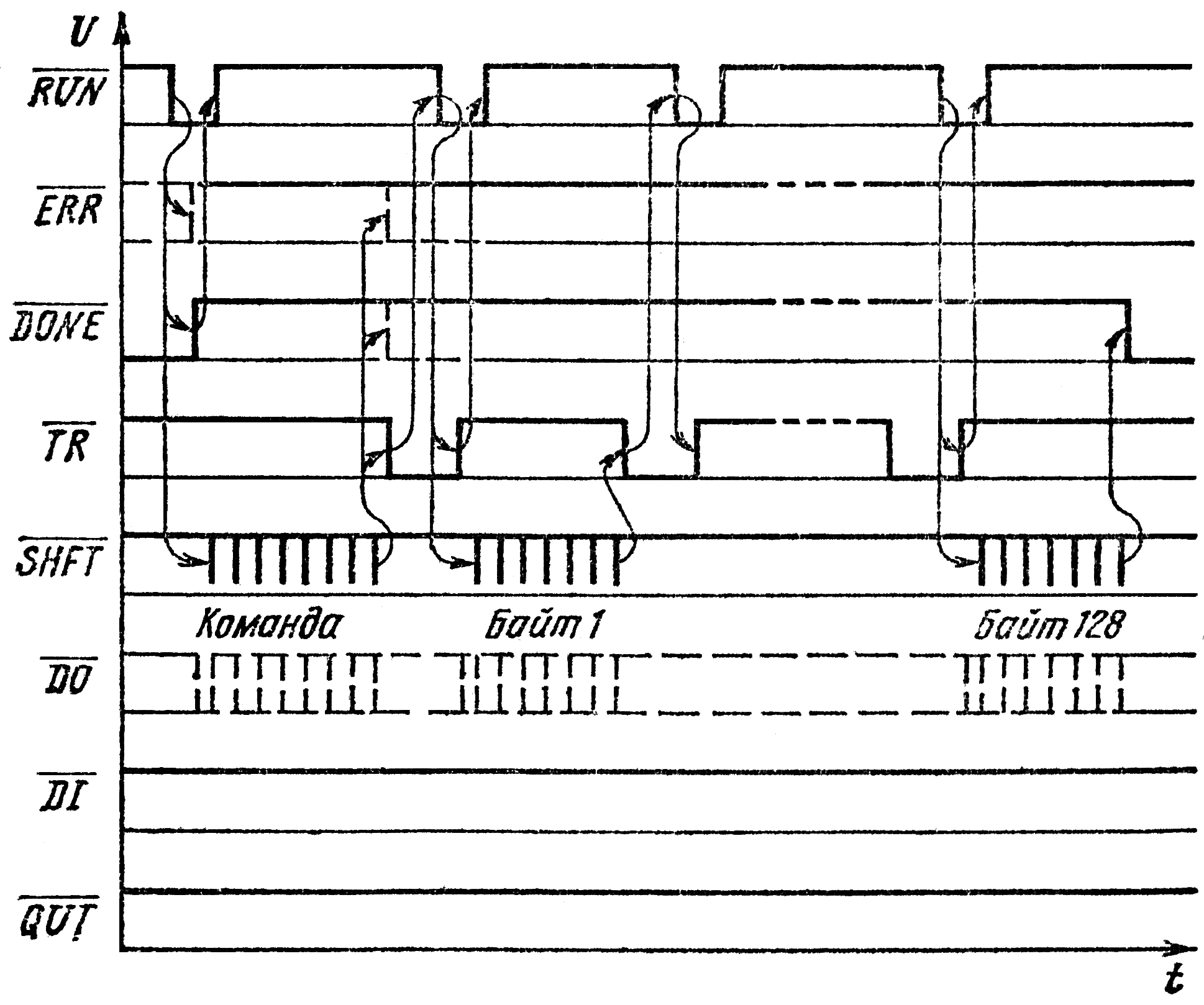

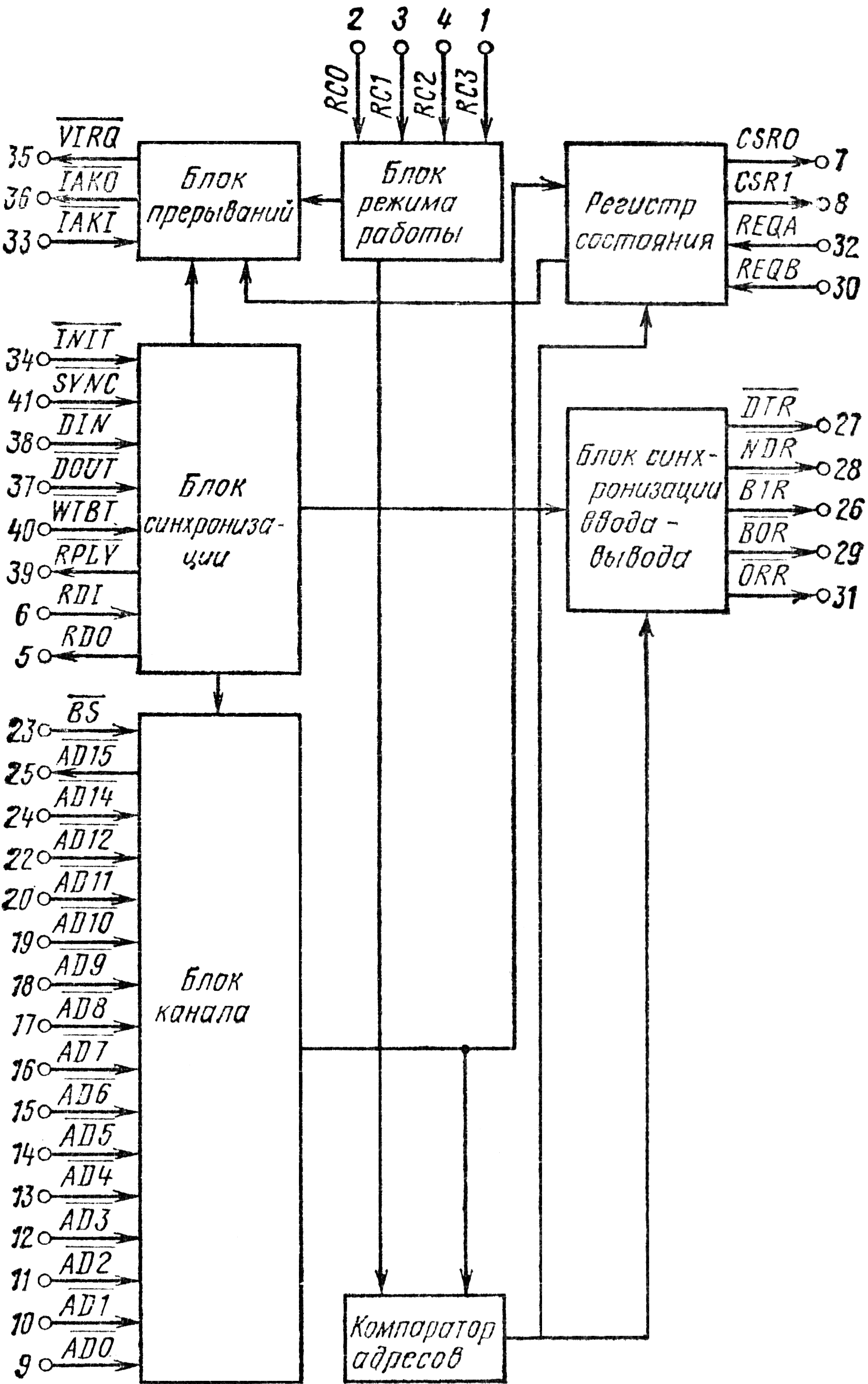

Условное графическое обозначение микросхемы К1801ВП1-033 в этом режиме приведено на рис. 1, назначение выводов показано в табл. 1, электрическая структурная схема представлена на рис. 2.

|

|

|

|

Рис. 1. Условное графическое обозначение микросхемы К1801ВП1-033 в режиме интерфейса накопителя на гибких магнитных дисках по порядку расположения (а) и функциональному назначению (б) выводов

|

|

|

Вывод |

Обозначение |

Тип вывода |

Наименование |

|---|---|---|---|

|

1 |

RC3 |

Вход |

Выбор режима 3 |

|

2 |

RC0 |

Вход |

Выбор режима 0 |

|

3 |

RC1 |

Вход |

Выбор режима 1 |

|

4 |

RC2 |

Вход |

Выбор режима 2 |

|

5 |

RC4 |

Вход |

Выбор режима 4 |

|

6 |

RC5 |

Вход |

Выбор режима 5 |

|

7 |

SHFT |

Вход |

Сдвиг данных |

|

8 |

OUT |

Вход |

Вывод данных |

|

9...16 |

AD0 ... AD7 |

Вход-выход |

Разряды адреса-данных |

|

17...20 |

AD8 ... AD11 |

Вход |

То же |

|

21 |

GND |

- |

Общий |

|

22 |

AD12 |

Выход |

12-й разряд адреса-данных |

|

23 |

BS |

Выход |

Внешнее устройство |

|

24 |

AD14 |

Выход |

14-й разряд адреса-данных |

|

25 |

AD15 |

Выход |

15-й разряд адреса-данных |

|

26 |

DI |

Вход |

Вход данных |

|

27 |

DO |

Выход |

Выход данных |

|

28 |

RUN |

Выход |

Пуск |

|

29 |

SET |

Вход |

Начальная установка |

|

30 |

ERR |

Вход |

Ошибка |

|

31 |

DONE |

Вход |

Завершено |

|

32 |

TR |

Вход |

Требование передачи |

|

33 |

IAKI |

Вход |

Разрешение прерывания |

|

34 |

INIT |

Вход |

Установка |

|

35 |

VIRQ |

Выход |

Требование прерывания |

|

36 |

IAKO |

Выход |

Предоставление прерывания |

|

37 |

DOUT |

Вход |

Вывод данных |

|

38 |

DIN |

Вход |

Ввод данных |

|

39 |

RPLY |

Выход |

Ответ |

|

40 |

WTBT |

Вход |

Запись-байт |

|

41 |

SYNC |

Вход |

Обмен |

|

42 |

UCC |

- |

Напряжение источника питания |

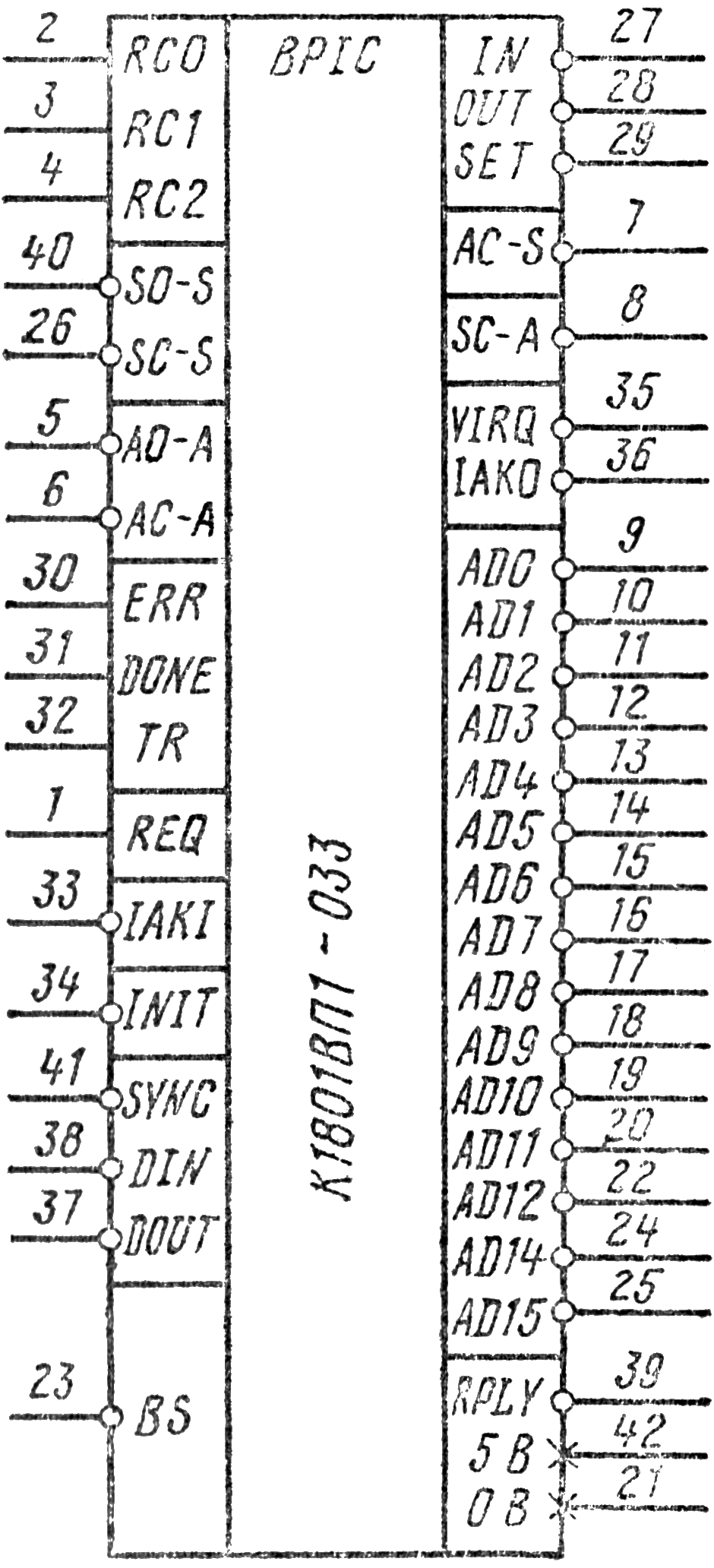

Рис. 2. Электрическая структурная схема интерфейса накопителя на гибких магнитных дисках

Микросхема устанавливается в этот режим подачей на выводы RC0 ... RC3 напряжения высокого уровня. Обмен информацией между процессором и контроллером НГМД осуществляется с помощью регистра команд состояния и регистра данных, которые считываются и загружаются программно. Формат регистра команд и состояния представлен на рис. 3. Разряды 08...13 не используются. Назначение остальных разрядов следующее:

GO (пуск) - инициирует приём команды (только для записи);

F1 ... F3 - коды команд (только для записи);

US (выбор привода) - выбор одного из двух дисководов для выполнения требуемой команды (только для записи);

DONE (завершено) - выполнение команды закончено (только для чтения);

IE (предоставление прерывания) - устанавливается программно для выполнения прерывания по окончании выполнения команды; сбрасывается канальным сигналом INIT (для чтения и записи);

TR (требование передачи) - требование записи-считывания данных через регистр РД (только для чтения);

INIT (начальная установка) - устанавливается программно для приведения НГМД в исходное состояние;

ERROR (ошибка) - формируется, если в процессе выполнения команды произошла ошибка (только для чтения).

Наименования команд регистра в соответствии с кодами F1 ... F3 приведены в табл. 2.

|

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

ERROR |

INIT |

|

|

|

|

|

|

TR |

IE |

DONE |

US |

F3 |

F2 |

F1 |

GO |

Рис. 3. Формат регистра команд и состояния

|

Код |

Команда |

||

|---|---|---|---|

|

F3 |

F2 |

F1 |

|

|

0 |

0 |

0 |

Запись в буфер |

|

0 |

0 |

1 |

Чтение буфера |

|

0 |

1 |

0 |

Запись сектора |

|

0 |

1 |

1 |

Чтение сектора |

|

1 |

0 |

0 |

Не используется |

|

1 |

0 |

1 |

Чтение регистра РОС |

|

1 |

1 |

0 |

Запись сектора с меткой |

|

1 |

1 |

1 |

Чтение регистра РОШ |

Формат регистра данных представлен на рис. 4. Разряды 0 ... 7 содержат данные для ввода-вывода. Разряды 8 ... 15 не используются. Ниже приведён перечень интерфейсных сигналов контроллера НГМД:

SET (начальная установка) - приводит механизм и электронную часть НГМД в исходное состояние;

DONE (завершено) - устанавливается при выполнении команды или в случае ошибки;

RUN (пуск) - инициирует передачу команды или байта данных;

OUT (вывод) - указывает направление передачи байта информации (при низком уровне сигнала информация передаётся от НГМД к микросхеме);

TR (запрос передачи) - устанавливает готовность контроллера НГМД к приёму-передаче байта информации;

DI (вход данных) - линия приёма последовательной информации;

DO (выход данных) - линия передачи последовательной информации;

SHFT (сдвиг) - линия синхронизации приёма-передачи последовательной информации; длительность отрицательного импульса не менее 200 нс, период 1 мкс;

FRR (ошибка) - формируется при обнаружении ошибки; прекращает выполнение текущей команды и устанавливает сигнал DONE.

|

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

|

|

|

|

|

|

|

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Рис. 4. Формат регистра данных

Переадресация регистров. С помощью выводов RC4 и RC5 можно переадресовать регистры микросхемы. Соответственно изменяются адреса векторов прерываний (табл. 3).

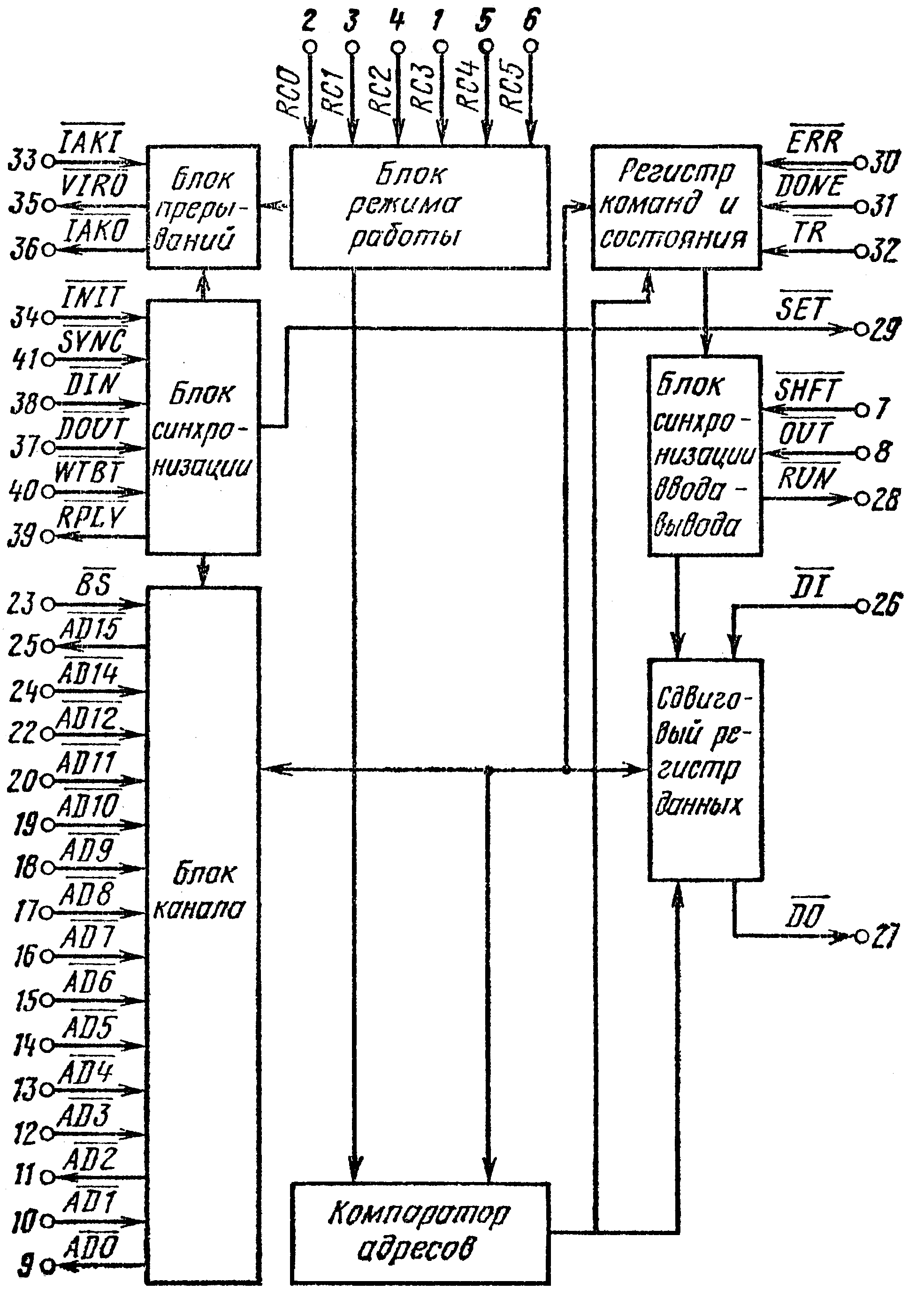

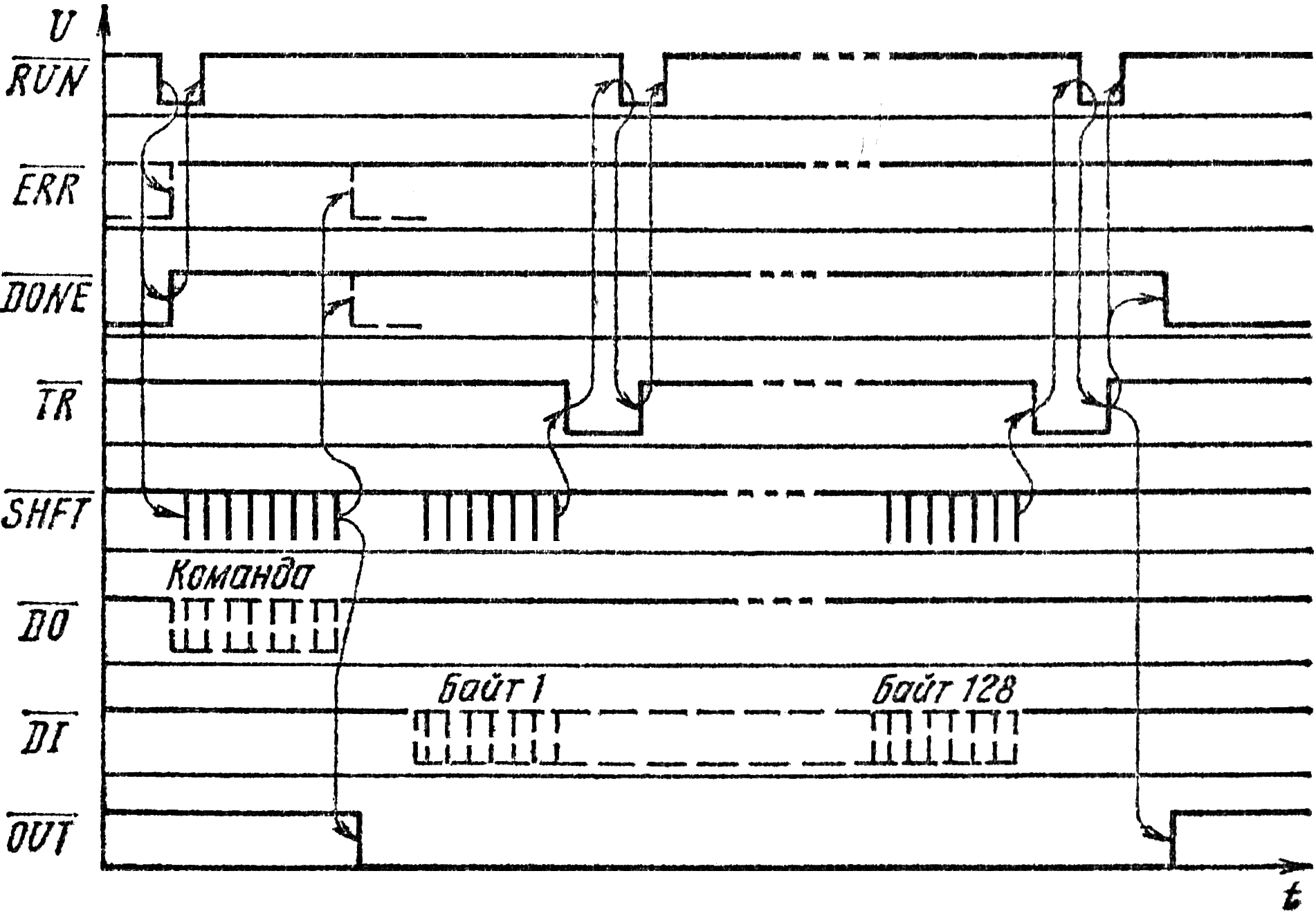

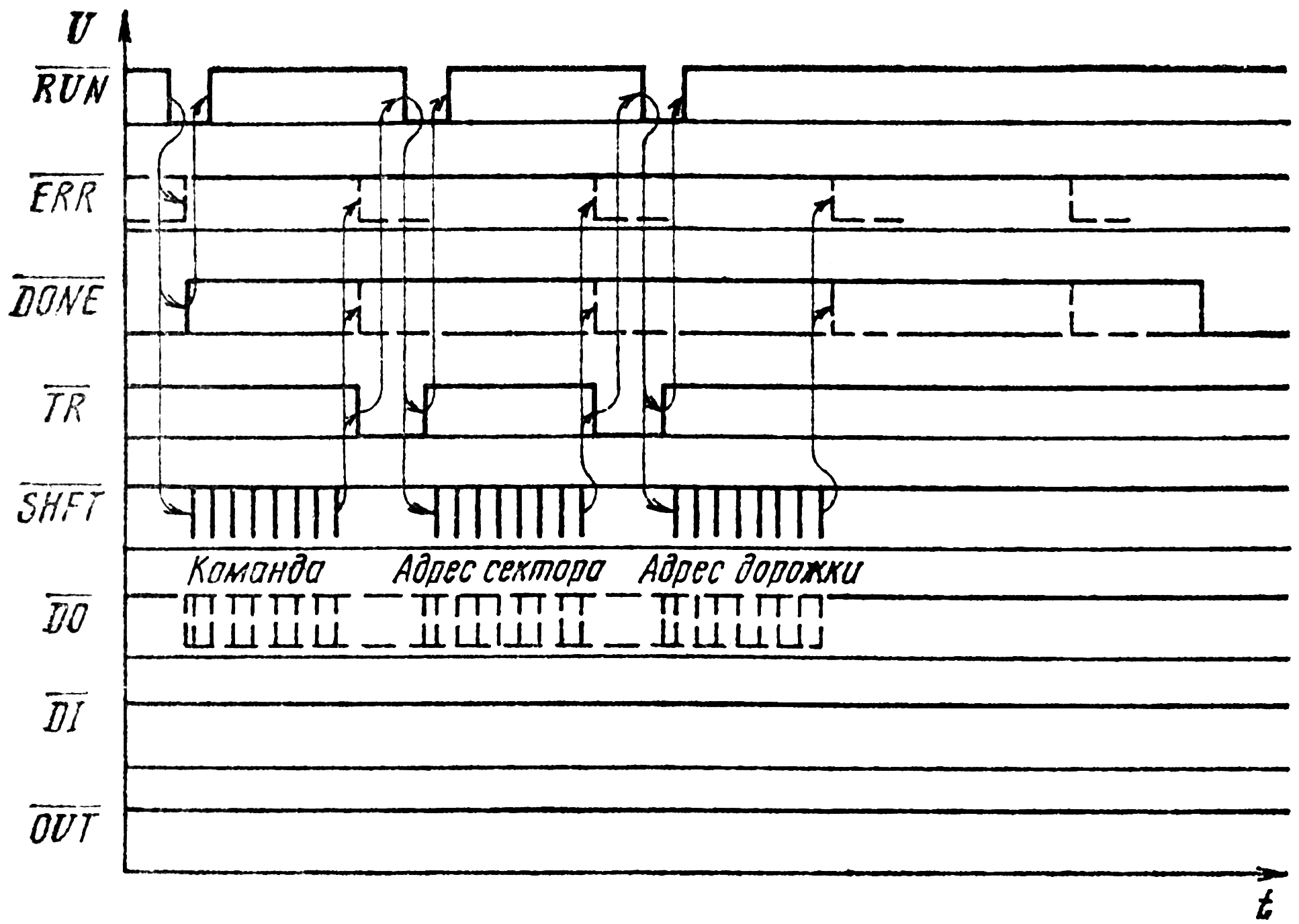

Работа микросхемы. При низком уровне сигнала DONE запись команды, содержащей Лог. 1 в нулевом разряде, в регистр команд устанавливает сигнал RUN, который инициирует контроллер НГМД на приём команды. Контроллер снимает DONE и выставляет на линию SHFT серию из восьми импульсов.

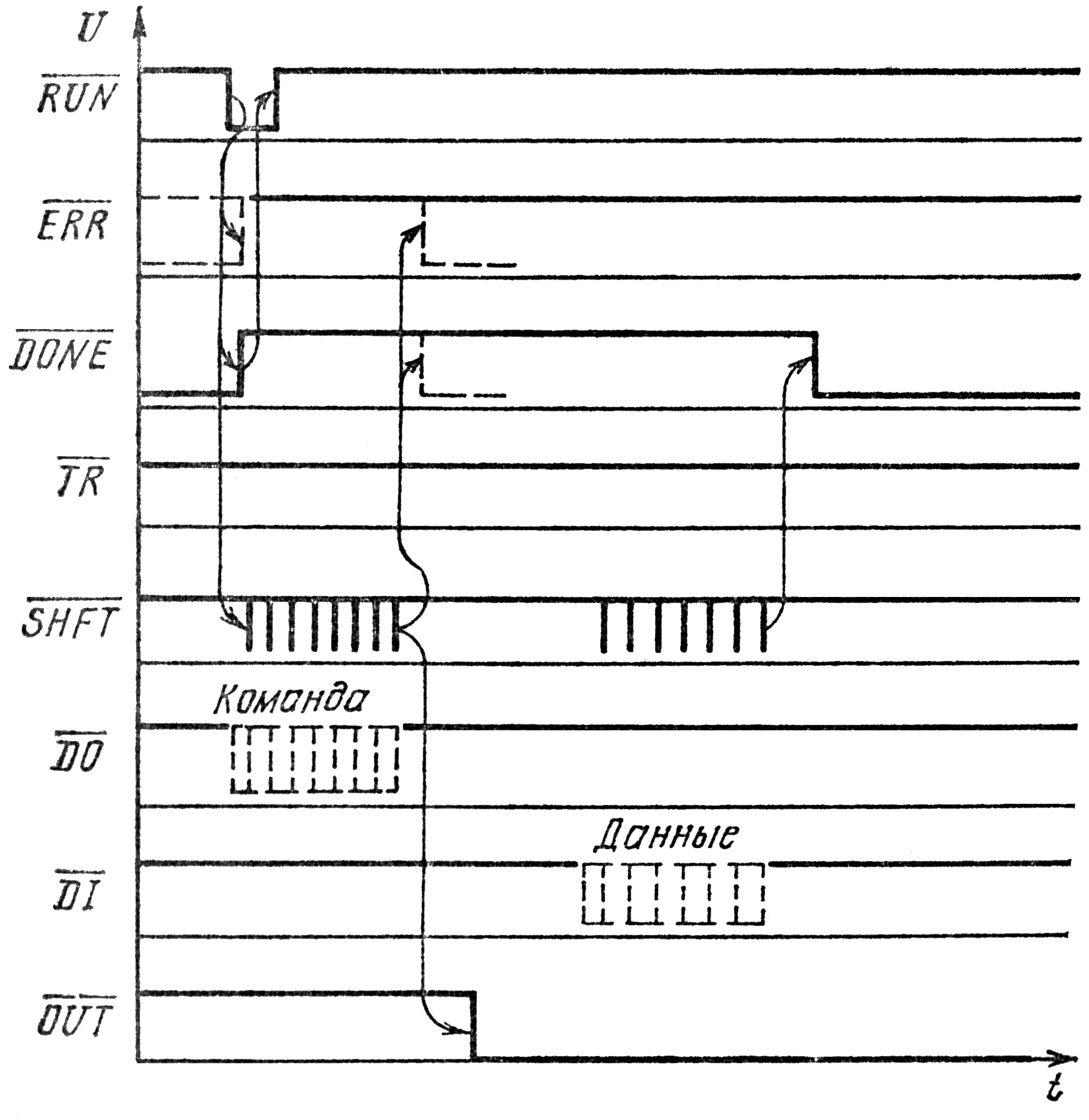

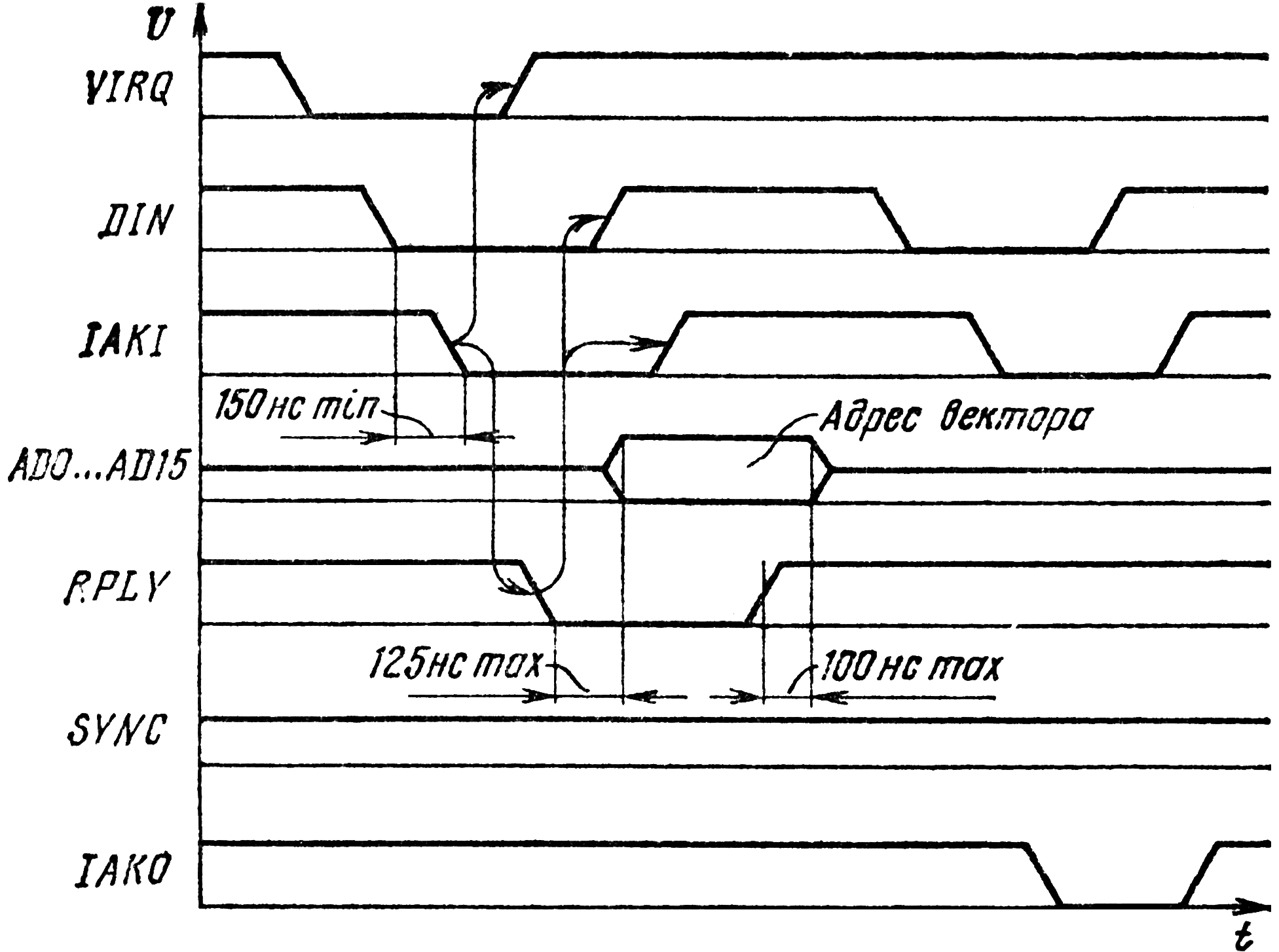

После снятия сигнала DONE происходит сброс сигнала RUN, а серия импульсов синхронизирует выдачу команды в последовательном коде на вывод DO. В зависимости от принятого кода команды контроллер вырабатывает сигналы OUT и TR (рис. 5-8). При установленном сигнале TR в зависимости от состояния сигнала OUT обращение к регистру вызывает сигнал RUN, который сбрасывается после снятия сигнала TR, и серию импульсов на выводе SHFT (восемь импульсов для синхронизации адреса сектора и дорожки, семь - для синхронизации данных). По окончании выполнения команды формируется сигнал DONE, который используется для работы по прерыванию (рис. 9). Требование прерывания VIRQ возникает с появлением сигнала DONE при наличии в регистре команд разрешения прерывания IE.

|

Вывод |

Уровень сигнала |

Адрес РК |

Адрес РД |

Адрес вектора прерываний |

|---|---|---|---|---|

|

RC4 RC5 |

Низкий Низкий |

177170

|

177172

|

264

|

|

RC4 RC5 |

Высокий Низкий |

177174 |

177176 |

270 |

|

RC4 RC5 |

Низкий Высокий |

177200

|

177202

|

274

|

|

RC4 RC5 |

Высокий Высокий |

ХХХХХ0 |

ХХХХХ2 |

XXX |

Примечание. X - значение разрядов адреса безразлично

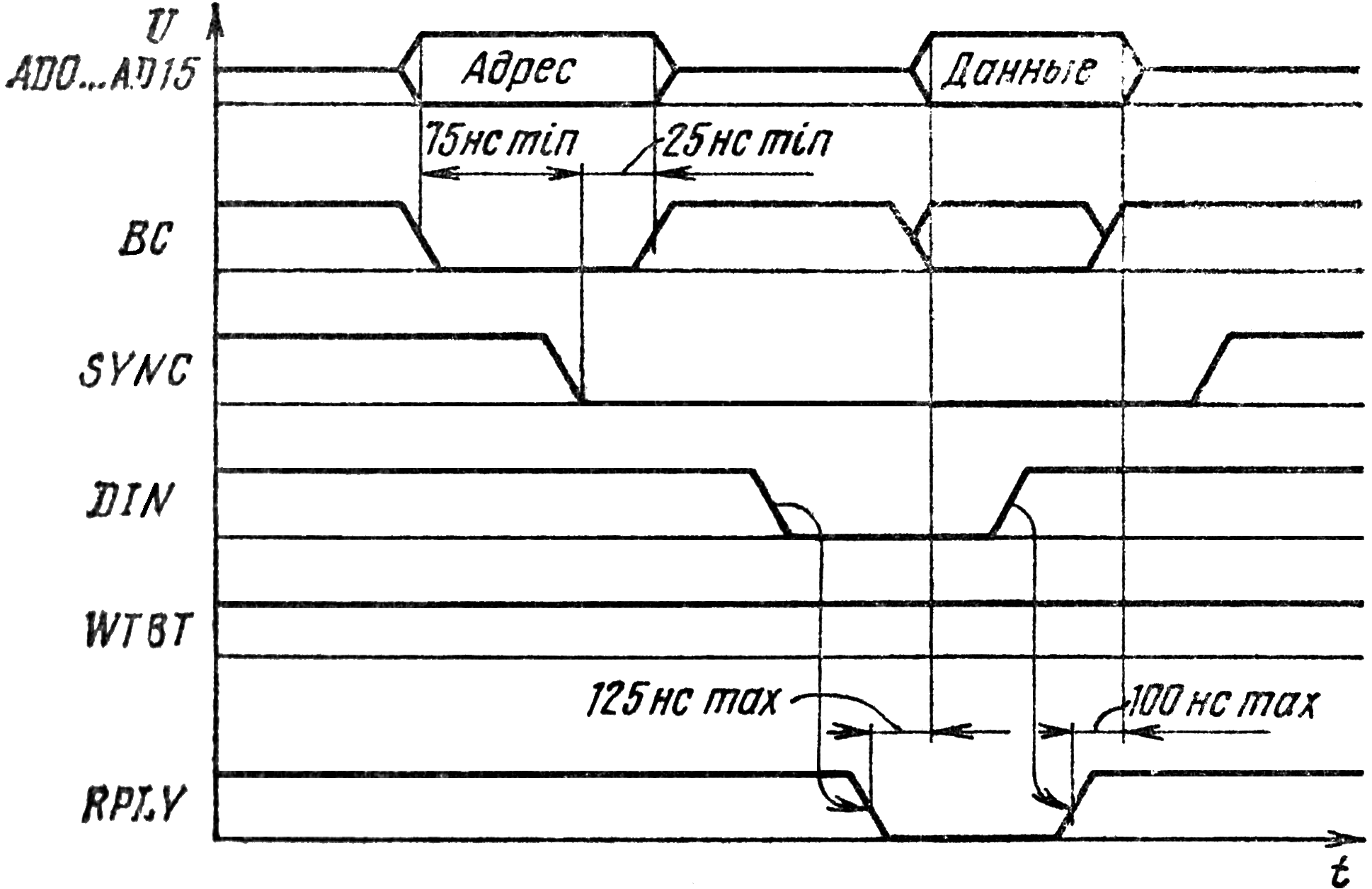

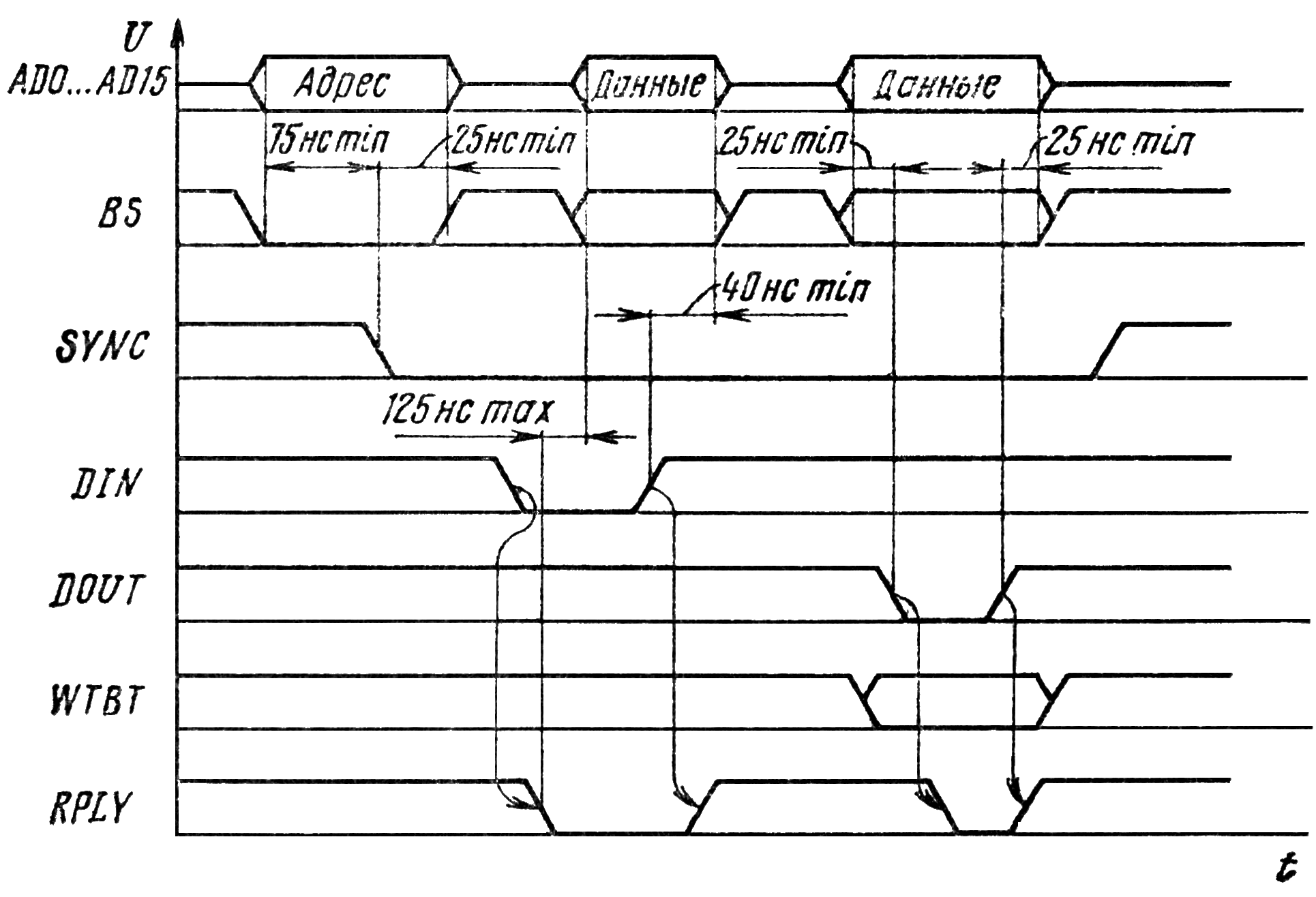

Рис. 5. Временная диаграмма цикла «запись в буфер»

Рис. 6. Временная диаграмма цикла «чтение буфера»

Рис 7. Временная диаграмма циклов «запись сектора», «чтение сектора»

Рис 8. Временная диаграмма циклов «считывание регистра состояния и ошибок», «считывание регистра ошибок»

Рис. 9. Временная диаграмма работы по прерыванию программы

Режим интерфейса параллельного ввода-вывода

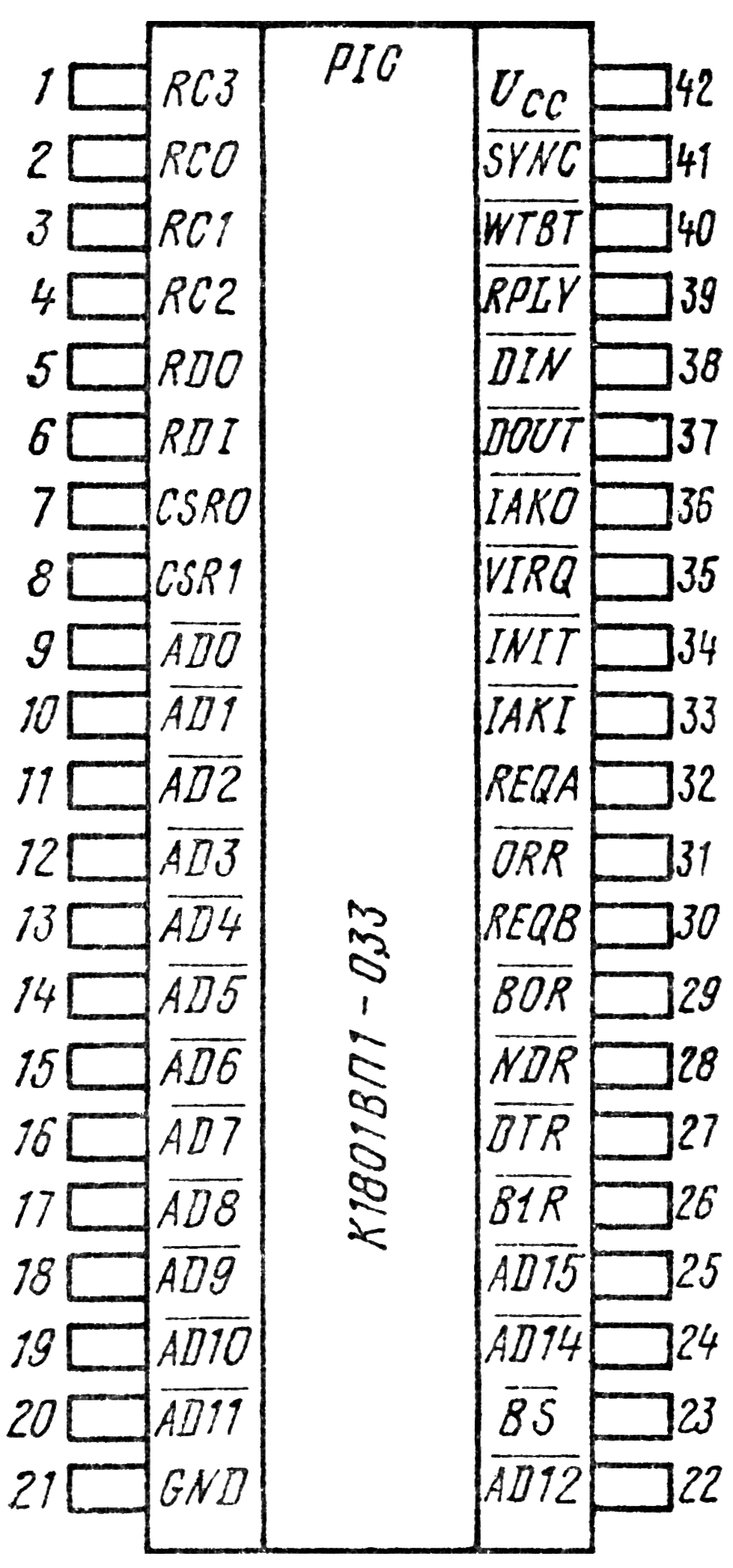

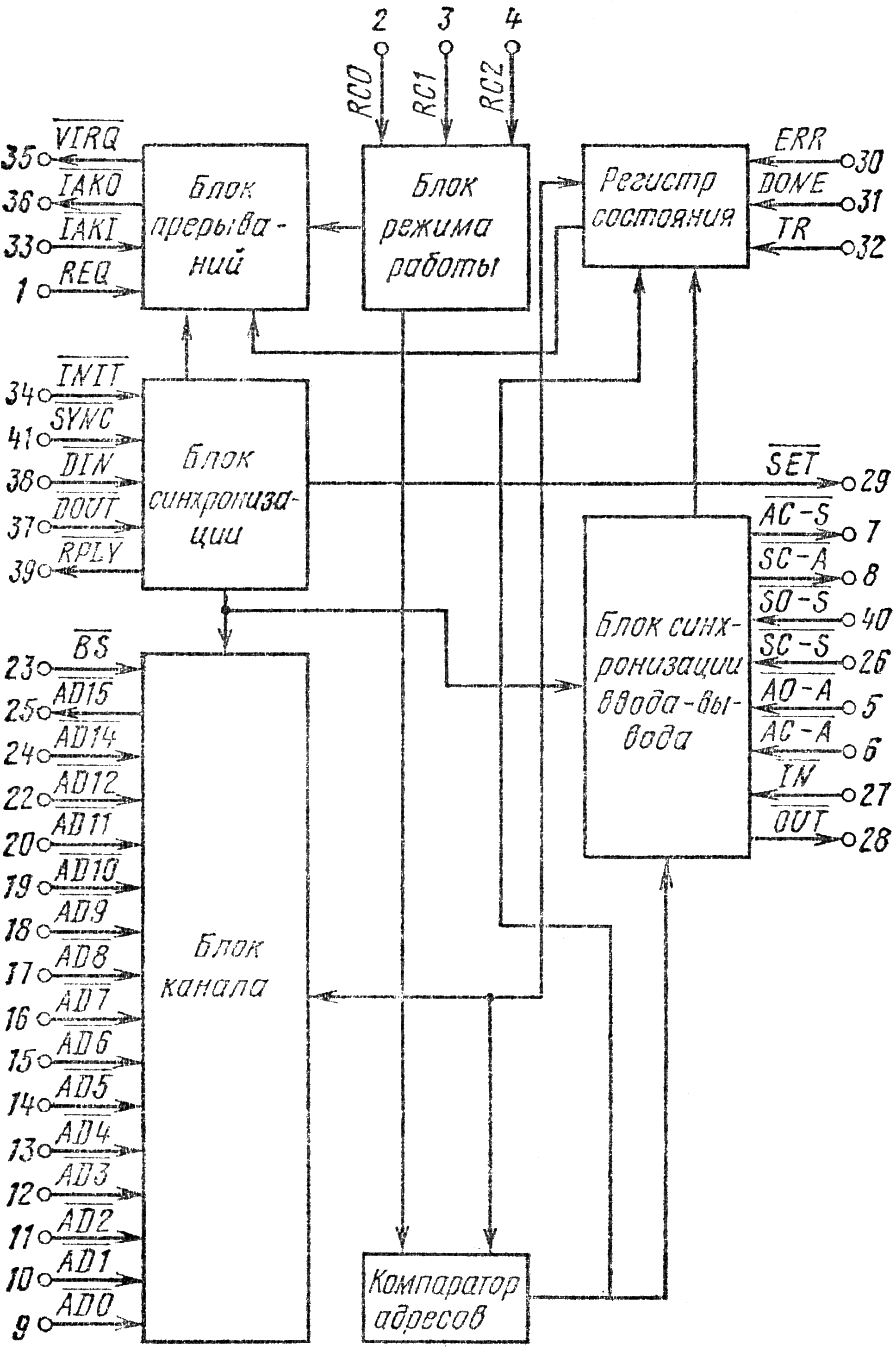

Условное графическое обозначение микросхемы в этом режиме приведено на рис. 10, назначение выводов показано в табл. 4, электрическая структурная схема представлена на рис. 11. В этот режим микросхема переводится подачей определённых уровней напряжения на выводы RC0... RC3. Кроме выбора режима работы комбинация напряжений определяет переадресацию регистров и векторов прерываний (табл. 5).

|

|

|

|

Рис. 10. Условное графическое обозначение микросхемы К1801ВП1-033 в режиме контроллера интерфейса параллельного ввода-вывода по порядку расположения (а) и функциональному назначению (б) выводов |

|

|

Вывод |

Обозначение |

Тип ввода |

Наименование |

|---|---|---|---|

|

1 |

RC3 |

Вход |

Выбор режима 3 |

|

2 |

RC0 |

Вход |

Выбор режима 0 |

|

3 |

RC1 |

Вход |

Выбор режима 1 |

|

4 |

RC2 |

Вход |

Выбор режима 2 |

|

5 |

RDO |

Выход |

Задержка ответа |

|

6 |

RDI |

Вход |

Задержка ответа |

|

7 |

CSR0 |

Выход |

Регистр состояния PC0 |

|

8 |

CSR1 |

Выход |

Регистр состояния PC1 |

|

9...16 |

AD0... AD7 |

Вход-выход |

Разряды адреса-данных |

|

17...20 |

AD8 ...AD11 |

Вход |

То же |

|

21 |

GND |

- |

Общий |

|

22 |

AD12 |

Вход |

12-й разряд адреса-данных |

|

23 |

BS |

Вход |

Внешнее устройство |

|

24 |

AD14 |

Вход |

14-й разряд адреса-данных |

|

25 |

AD15 |

Вход |

15-й разряд адреса данных |

|

26 |

B1R |

Выход |

Вывод старшего байта |

|

27 |

DTR |

Выход |

Ввод данных |

|

28 |

NDR |

Выход |

Вывод данных |

|

29 |

B0R |

Выход |

Вывод младшего байта |

|

30 |

REQB |

Вход |

Требование В |

|

31 |

ORR |

Выход |

Чтение выходного регистра |

|

32 |

REQA |

Вход |

Требование А |

|

33 |

IAKI |

Вход |

Предоставление прерывания |

|

34 |

INIT |

Вход |

Установка |

|

35 |

VIRQ |

Выход |

Требование прерывания |

|

36 |

IAKO |

Выход |

Предоставление прерывания |

|

37 |

DOUT |

Вход |

Вывод данных (по каналу) |

|

38 |

DIN |

Вход |

Ввод данных (по каналу) |

|

39 |

RPLY |

Выход |

Ответ |

|

40 |

WTBT |

Вход |

Запись-байт |

|

41 |

SYNC |

Вход |

Обмен |

|

42 |

UCC |

- |

Напряжение источника питания |

Рис. 11. Электрическая структурная схема контроллера интерфейса параллельного ввода-вывода

|

Вывод |

Уровень сигнала |

Адрес PC |

Адрес РИ |

Адрес РП |

Адрес вектора прерывания |

|

|---|---|---|---|---|---|---|

|

А |

В |

|||||

|

RC3 RC0 RC1 RC2 |

Низкий Высокий Низкий Высокий |

167770

|

167772

|

167774

|

А В

|

300 304

|

|

RC3 RC0 RC1 RC2 |

Высокий Высокий Низкий Высокий |

167760

|

167762

|

167764

|

А В

|

310 314

|

|

RC3 RC0 RC1 RC2 |

Низкий Низкий Высокий Высокий |

167750

|

167752

|

167754

|

А В

|

320 324

|

|

RC3 RC0 RC1 RC2 |

Высокий Низкий Высокий Высокий |

167740

|

167442

|

167744

|

А В

|

330 334

|

|

RC3 RC0 RC1 RC2 |

Низкий Высокий Высокий Высокий |

ХХХХХ0

|

ХХХХХ2

|

ХХХХХ4

|

А В

|

ХХ0 ХХ4

|

Микросхема К1801ВП1-033 осуществляет приём и передачу информации с помощью регистров состояния PC, приёмника РП и источника РИ. Регистры РП и РИ выполняются на двух микросхемах К1801ВП1-034 (описание БИС будет в следующем номере). БИС К1801ВП1-033 содержит PC, компаратор адресов, блок прерываний и блок управления регистрами РП и РИ. Формат регистра состояния представлен на рис. 12. Назначение разрядов PC следующее:

CSR1, CSR0, (РС01, PC00) - используются для имитации запросов прерывания в режиме автономной проверки (для чтения и записи);

REQA (требование А) - требование прерывания А (только для чтения);

REQB (требование В) - требование прерывания В (только для чтения);

IEA (разрешение А) - разрешение прерывания А, сбрасывается сигналом INIT (для чтения и записи);

IEB (разрешение В) - разрешение прерывания В, сбрасывается сигналом INIT (для чтения и записи).

|

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

REQB |

|

|

|

|

|

|

|

REQA |

IEA |

IEB |

|

|

|

CSR1 |

CSR0 |

Рис. 12. Формат регистра состояния

Сигналы управления регистрами РП и РИ:

DTR (ввод данных) - чтение РП;

NDR (вывод данных) -запись в РП;

B1R (вывод старшего байта) -запись старшего байта в РИ;

B0R (вывод младшего байта)-запись младшего байта в РИ;

ORR (чтение выходного регистра) - чтение РИ;

RDO (задержка ответа, выход) - выход разрыва цепочки формирования сигнала RPLY;

RDI (задержка ответа, вход) - вход разрыва цепочки формирования сигнала RPLY.

С помощью RC-цепочки, включённой между выводами RDI и. RDO, можно увеличить ширину импульсов DTR и NDR.

Работа микросхемы по прерыванию. Запрос прерывания VIRQ возникает при появлении хотя бы одного из сигналов REQA, REQB при наличии в PC разрешения прерывания IEA, IEB. При одновременном появлении сигналов REQA и REQB более высокий приоритет имеет требование В. Процедура прерывания выполняется стандартно (см. рис. 9).

Режим контроллера байтового параллельного интерфейса

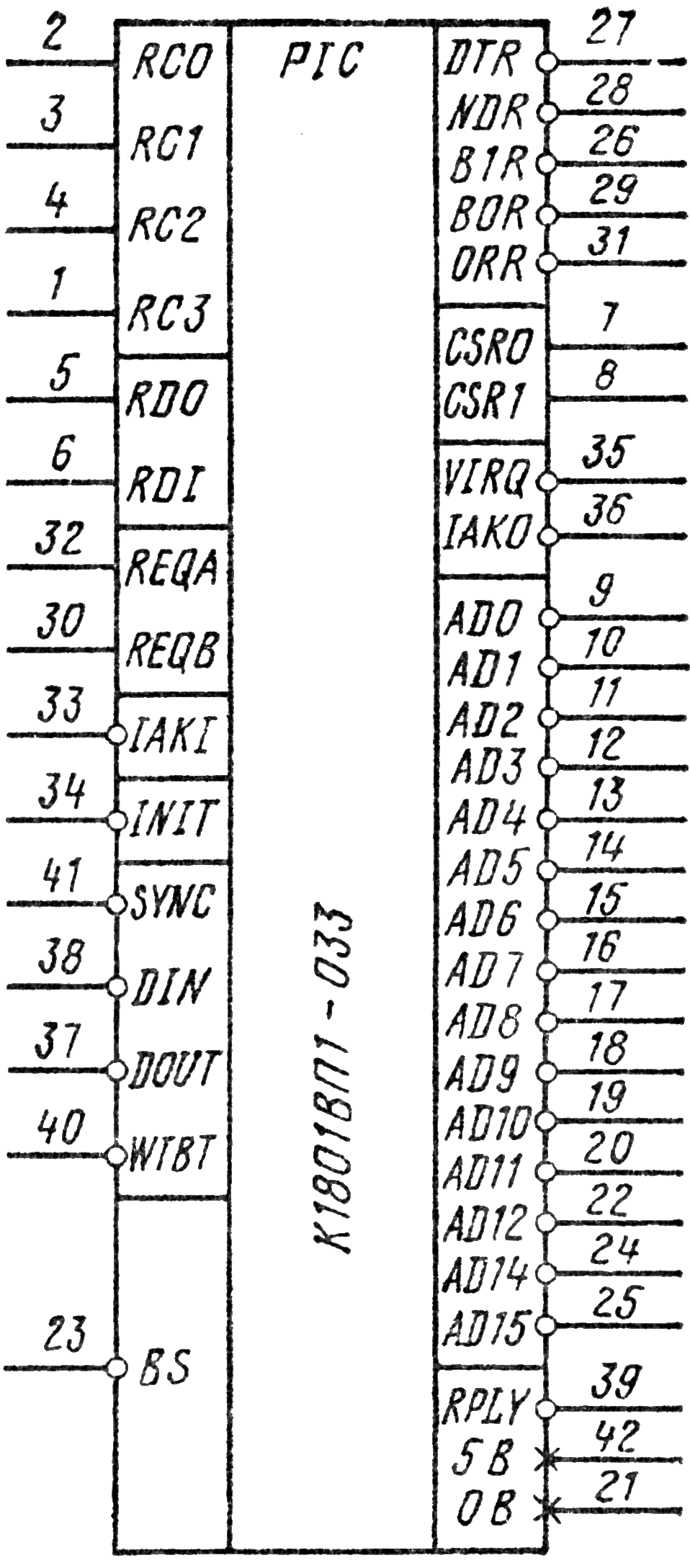

Условное графическое обозначение микросхемы в этом режиме дано на рис. 13, назначение выводов приведено в табл. 6, электрическая структурная схема представлена на рис. 14. Режим задаётся подачей напряжений определённого уровня на выводы RC0... RC2 (табл. 7). Приём и передача данных осуществляются с помощью регистров состояния источника РСИ и приёмника РСП, регистров источника РИС и приёмника РП. Регистры РИС и РП выполняются на одной микросхеме К1801ВП1-034, а БИС К1801ВП1-033 содержит регистры РСИ и РСП, компаратор адресов, блоки прерываний и управления регистрами РИС и РП.

|

|

|

|

Рис. 13. Условное графическое обозначение микросхемы К1801ВП1-033 в режиме контроллера байтового параллельного интерфейса по порядку расположения (а) и функциональному назначению (б) выводов |

|

|

Вывод |

Обозначение |

Тип вывода |

Наименование |

|---|---|---|---|

|

1 |

REQ |

Вход |

Требование |

|

2 |

RC0 |

Вход |

Выбор режима 0 |

|

3 |

RC1 |

Вход |

Выбор режима 1 |

|

4 |

RC2 |

Вход |

Выбор режима 2 |

|

5 |

АО-А |

Вход |

Готовность приёмника |

|

6 |

AC-A |

Вход |

Запрос приёмника |

|

7 |

AC-S |

Выход |

Запрос источника |

|

8 |

SC-A |

Выход |

Строб приёмника |

|

9...16 |

AD0 ... AD7 |

Вход-выход |

Разряды адреса-данных |

|

17...20 |

AD8 ... AD11 |

Вход |

То же |

|

21 |

GND |

- |

Общий |

|

22 |

AD12 |

Вход |

12-й разряд адреса-данных |

|

23 |

BS |

Вход |

Внешнее устройство |

|

24 |

AD14 |

Вход |

14-й разряд адреса-данных |

|

25 |

AD15 |

Выход |

15-й разряд адреса данных |

|

26 |

SC-S |

Вход |

Строб источника |

|

27 |

IN |

Вход |

Ввод данных |

|

28 |

OUT |

Выход |

Вывод данных |

|

29 |

SET |

Выход |

Начальная установка |

|

30 |

ERR |

Вход |

Ошибка |

|

31 |

DONE |

Вход |

Завершено |

|

32 |

TR |

Вход |

Требование передачи |

|

33 |

IAKI |

Вход |

Предоставление прерывания |

|

34 |

INIT |

Вход |

Установка |

|

35 |

VIRQ |

Выход |

Требование прерывания |

|

36 |

IAKO |

Выход |

Предоставление прерывания |

|

37 |

DOUT |

Вход |

Вывод данных (по каналу) |

|

38 |

DIN |

Вход |

Ввод данных (по каналу) |

|

39 |

RPLY |

Выход |

Ответ |

|

40 |

SO-S |

Вход |

Готовность источника |

|

41 |

SYNС |

Вход |

Обмен |

|

42 |

UСС |

- |

Напряжение источника питания |

|

Вывод |

Уровень сигнала |

Адрес РСИ |

Адрес РП |

Адрес РСП |

Адрес РИ |

Адрес вектора прерывания |

|---|---|---|---|---|---|---|

|

RC0 RC1 RC2 |

Низкий Низкий Низкий |

-

|

-

|

177514

|

177516

|

200

|

|

RC0 RC1 RC2 |

Высокий Низкий Низкий |

177560

|

177562

|

177554

|

176566

|

И 60 П 64

|

|

RC0 RC1 RC2 |

Низкий Высокий Низкий |

177550

|

177552

|

177554

|

177556

|

И 70 П 74 |

|

RC0 RC1 RC2 |

Высокий Высокий Низкий |

177570

|

177572

|

177574

|

177576

|

И 170 П 174 |

|

RC0 RC1 RC2 |

Низкий Низкий Высокий |

ХХХХХ0

|

ХХХХХ2

|

ХХХХХ4

|

ХХХХХ6

|

И XX0

П ХХ4 |

Рис. 14. Электрическая структурная схема контроллера байтового параллельного интерфейса

|

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

ERR |

|

|

|

|

|

|

|

AR |

IEA |

|

|

|

|

|

|

Рис. 15. Формат регистра состояния источника

|

15 |

14 |

13 |

12 |

11 |

10 |

09 |

08 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

ERR |

SET |

|

|

|

|

|

|

TR |

IET |

|

DONE |

|

|

|

|

Рис. 16. Формат регистра состояния приёмника

Формат регистра состояния источника показан на рис. 15. Назначение отдельных разрядов следующее:

IEA - разрешение прерывания по приёму; сбрасывается сигналом INIT (для чтения и записи);

AR - требование приёма (только для чтения);

ERR - ошибка (только для чтения).

Формат регистра состояния приёмника представлен на рис. 16. Назначение разрядов, обозначенных на рисунке, следующее:

DONE - завершено (только для чтения);

IET - разрешение прерывания по передаче; сбрасывается канальным сигналом INIT (для чтения и записи);

TR - требование передачи (только для чтения); SET - начальная установка (только для записи);

ERR - ошибка (только для чтения).

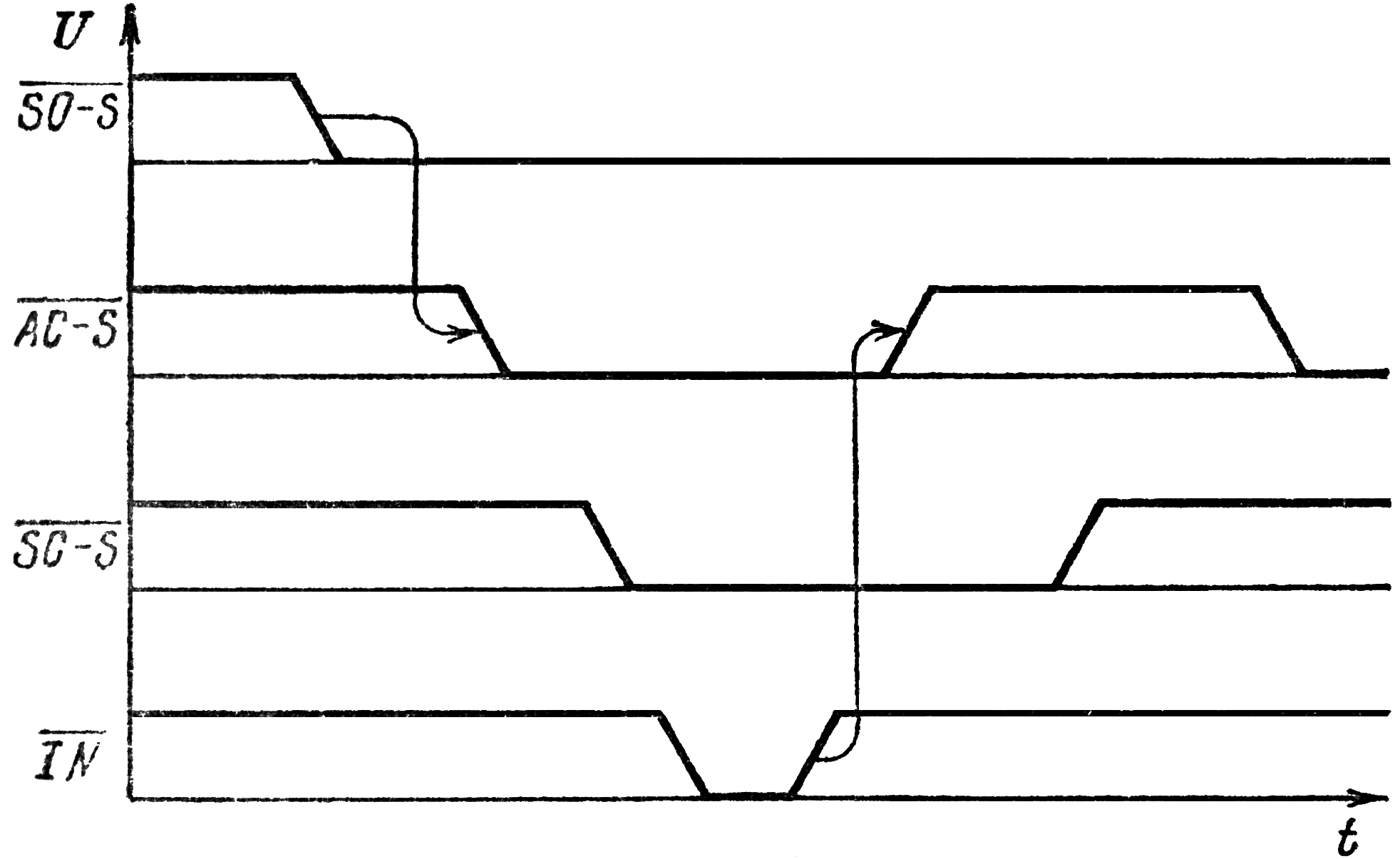

Работа микросхемы на приём информации (рис. 17). В рабочее состояние микросхема переводится сигналом SO-S. При появлении этого сигнала вырабатывается сигнал AC-S (запрос источника), ответом на который служит сигнал SC-S (строб источника). При поступлении последнего устанавливается бит AR (требование приёма) в регистре состояния источника, который при наличии бита IEA (разрешение прерывания по приёму) вызывает запрос прерывания. В цикле чтения регистра приёмника вырабатывается сигнал IN (ввод данных) и снимается сигнал AC-S. Вновь установиться сигнал AC-S может только после снятия сигнала SC-S. При отсутствии сигнала SO-S (готовность источника) в регистре РСИ установлен бит ERR - микросхема к работе не готова.

Рис. 17. Временная диаграмма цикла «приём данных»

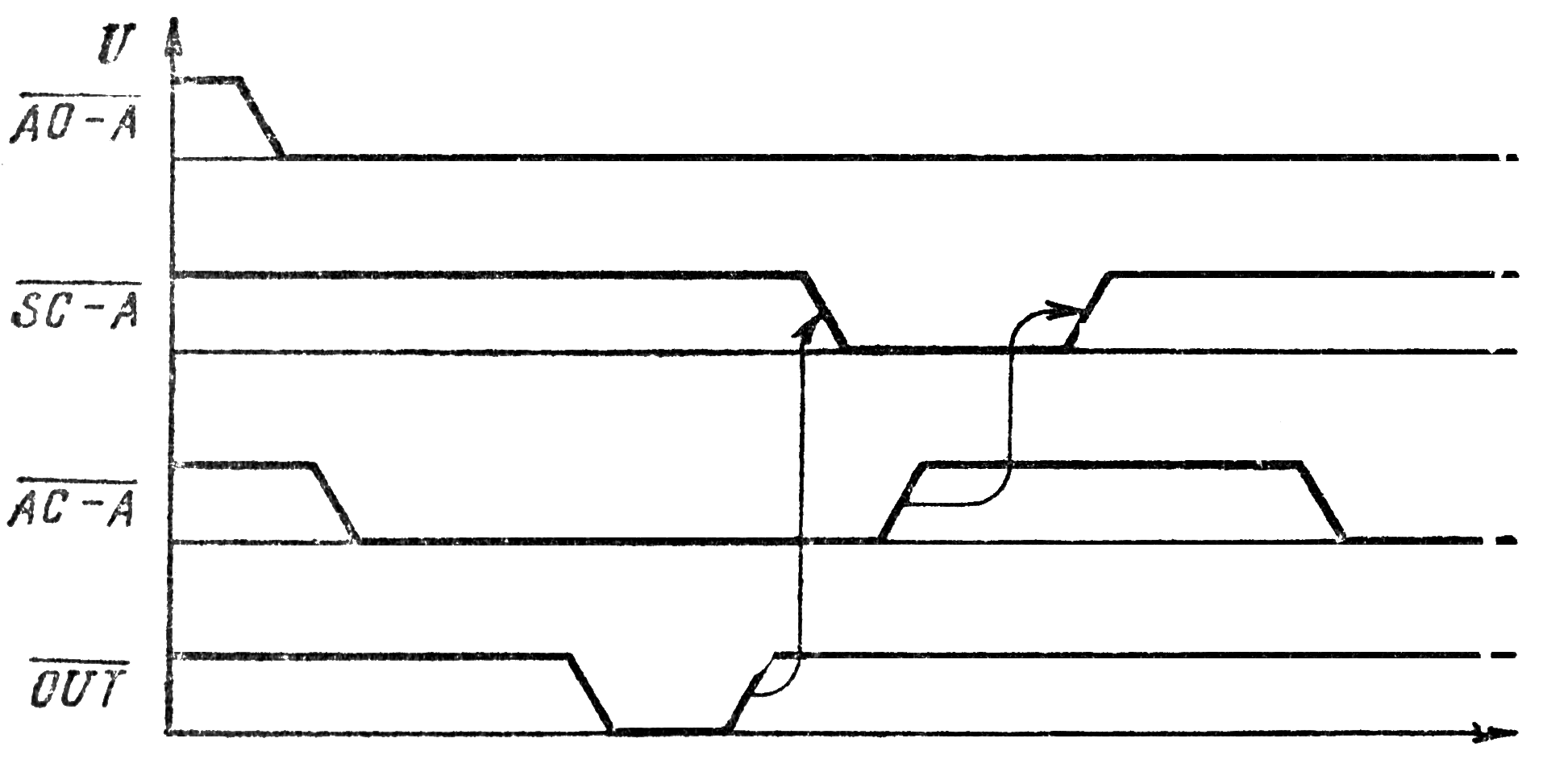

Работа микросхемы на передачу информации (рис. 18). Готовность к передаче данных наступает при наличии сигналов АО-А (готовность приёмника) и AC-A (запрос приёмника). После записи данных в регистр источника микросхема вырабатывает сигнал SC-А (строб приёмника), который сбрасывается после снятия сигнала AC-A. Во время записи в регистр источника устанавливается сигнал OUT (вывод данных).

Рис. 18. Временная диаграмма цикла «передача данных»

Рис. 19. Временная диаграмма цикла «ввод»

Рис. 20. Временная диаграмма цикла «вывод»

Рис. 21. Временная диаграмма цикла «ввод-пауза-вывод»

Состояния сигналов ERR, DONE, TR регистра состояния приёмника соответствуют состояниям одноименных сигналов приёмника. Запрос на прерывание по передаче данных возникает по сигналу REQ (требование) к установленному биту IET (разрешение прерывания по передаче) в регистре состояния.

Путём внешнего соединения вывода REQ с каким-либо выводом состояния приёмника можно вызвать запрос по любому состоянию приёмника. Запись Лог. 1 в разряд 14 регистра состояния приёмника и канальный сигнал INIT вызывают сигнал SET (начальная установка).

Основные циклы работы микросхемы К1801ВП1-033 иллюстрируются временными диаграммами, приведёнными на рис. 19-21. Обозначение Т соответствует передатчику, R - приёмнику.

При использовании микросхемы выводы на периферийные устройства необходимо развязывать буферными ТТЛ-элементами. Допустимое значение электростатического потенциала не более 100 В. Рекомендуемые схемы подключения микросхем К1801ВП1-033 и К1801ВП1-034 при совместной работе будут приведены после описания всех интерфейсных БИС комплекта.

Г.Г. Глушкова

Телефон 208-73-23, Москва