УДК 681.323

Р.И. Волков, В.П. Горский, В.Л. Дшхунян, С.С. Коваленко. П.Р. Машевич

ОДНОКРИСТАЛЬНЫЙ МИКРОПРОЦЕССОР КМ1801ВМ3

Микросхема КМ1801ВМ3 - однокристальный 16-разрядный микропроцессор, предназначенный для обработки цифровой информации в устройствах широкого применения. В составе ЭВМ микропроцессор может использоваться для решения инженерно-технических задач, управления технологическими процессами, станками ЧПУ, решения задач автоматизации проектирования.

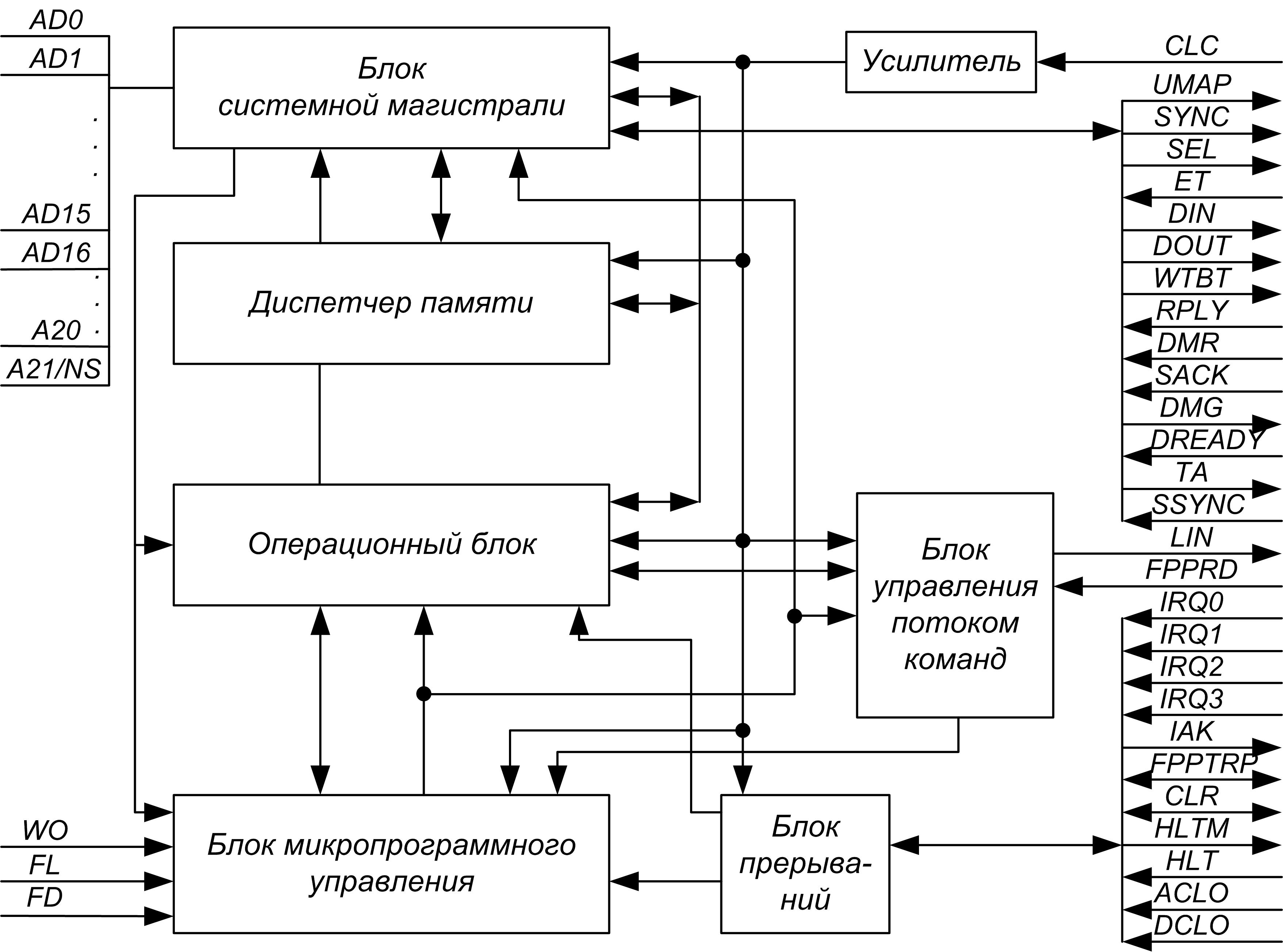

Рис. 1. Структурная схема микропроцессора КМ1801ВМ3

Структурная схема микропроцессора приведена на рис. 1. Работа основных блоков процессора - операционного, микропрограммного управления, диспетчера памяти и системной магистрали - совмещена во времени. В режиме «конвейерного» выполнения команд возможно одновременное выполнение до четырёх процессов: i-й команды в операционном блоке, формирование первой микрокоманды для (i+l)-й команды в блоке микропрограммного управления, чтение из памяти (i+2)-й команды в блоке системной магистрали, формирование физического адреса (i+3)-й команды в диспетчере памяти.

В блоке микропрограммного управления вырабатывается последовательность 30-разрядных микрокоманд, управляющих работой всех блоков. В его составе имеется две программируемые логические матрицы - ПЛМ предварительного разбора команд и основная ПЛМ. Первая быстродействующая ПЛМ позволяет параллельно с загрузкой кода команды формировать начальный адрес микропрограммы в основной ПЛМ. Наличие ПЛМ разбора команд, а также аппаратно реализованного сумматора - счётчика команд позволило сократить объём памяти основной ПЛМ и уменьшить число микрокоманд, необходимых для выполнения одной команды.

В операционном блоке формируются виртуальные адреса и операнды, выполняются логические и арифметические операции над операндами, хранятся операнды и результаты операций в регистрах, формируются и хранятся признаки результата операций. Передача информации в этот блок осуществляется по двум шинам чтения и отдельной шине записи, что позволило при наличии быстродействующего АЛУ сократить время цикла работы блока. Команды умножения, деления, параметрических сдвигов выполняются с помощью регистра - счётчика тактов, что уменьшило время исполнения команд расширенной арифметики по сравнению с чисто микропрограммным способом.

Диспетчер памяти даёт возможность увеличить объём адресуемой памяти до 4М байт, осуществить преобразование виртуальных адресов в физические и защиту памяти в системах с разделением времени, использовать различные области адресов для режимов пользователя и операционной системы. При работе процессора в конвейерном режиме цикл преобразования виртуального адреса в физический оказывается «скрытым» и не вызывает увеличения общего цикла работы.

В блоке прерываний осуществляется приём сигналов прерываний, их предварительная обработка и формирование адреса вектора прерывания.

Блок управления потоком команд синхронизирует работу блоков при приёме и обработке информации в «поточном» режиме, когда параллельно во времени выполняется инкрементирование счётчика команд для выборки (1+3)-й команды, преобразование виртуального значения счётчика для выборки (i+2)-й команды, загрузка физического значения счётчика в буфер системной магистрали для выборки (i+1)-й команды, приём i-й команды на вход ПЛМ разбора команд.

Блок системной магистрали осуществляет связь между внутренними магистралями данных и физического адреса и системной магистралью «адрес-данные», запись и чтение регистров ДП и слова состояния процессора, арбитраж устройств системной магистрали, связь с процессором обработки чисел в форме плавающей запятой (процессор плавающей запятой).

Ниже приведены основные технические характеристики микропроцессора:

|

Технические характеристики микропроцессора КМ1801ВМ3 |

|

|

Представление чисел |

дополнительный кол с фиксированной запятой |

|

Виды адресации |

регистровая, косвенно-регистровая. автоинкрементная. косвенно-автоинкрементная, автодекрементная, косвенно-автодекрементная, индексная, косвенно-индексная |

|

Число регистров общего назначения |

8 |

|

Число уровней прерывания |

4 |

|

Системная магистраль |

Типа МПИ |

|

Адресное пространство, М байт |

До 4 |

|

Тактовая частота, МГц |

До 6 |

|

Максимальное быстродействие при выполнении регистровых операций, млн операций/с |

2 |

|

Потребляемая мощность, Вт |

2 |

|

Напряжение питания, В |

+5 ±5% |

|

Уровни логических сигналов, В: |

|

|

«Лог. 0», менее |

0,5 |

|

«Лог. 1», более |

2,4 |

|

Нагрузочная способность по току, мА: |

|

|

«Лог. U», не менее |

3,2 |

|

«Лог. 1», не менее |

0,2 |

|

Технология изготовления |

n-МОП |

|

Конструкция |

64-выводной металлокерамический, типа Dip |

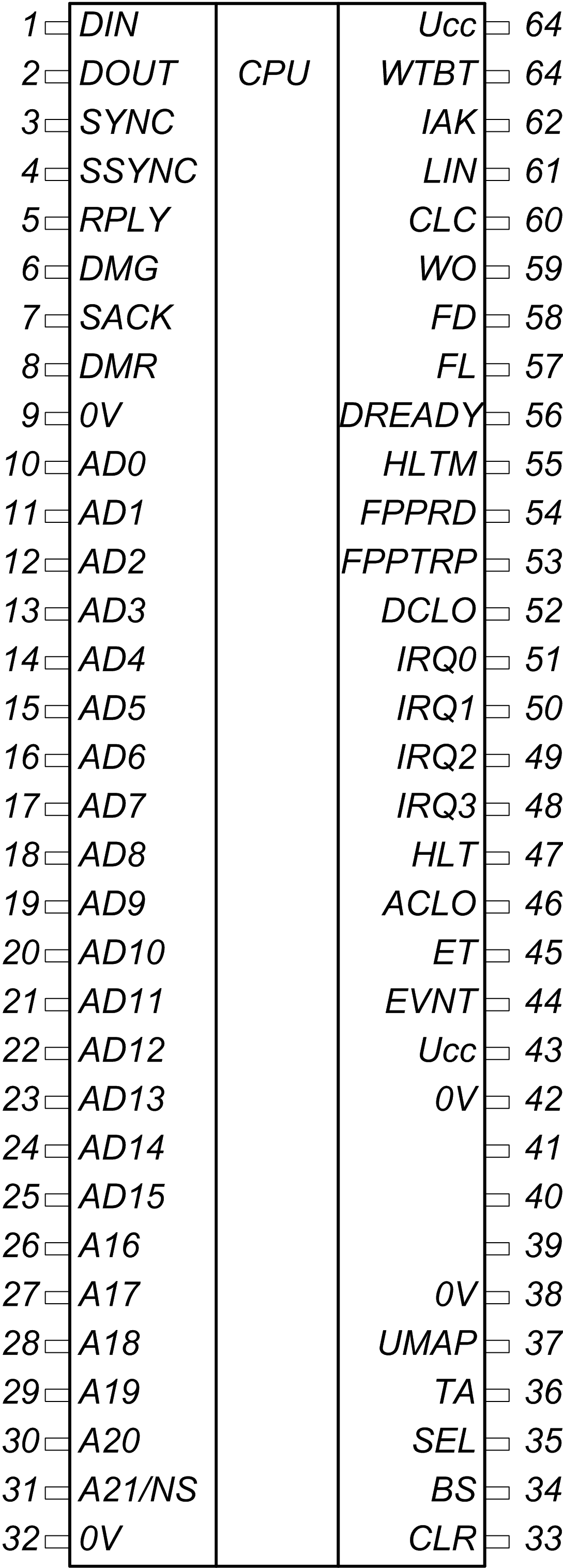

Система команд (табл. 1), реализованная в блоке микропрограммного управления, соответствует системе команд мини-ЭВМ «Электроника 100/25». Условно-графическое обозначение микросхемы приведено на рис. 2, наименование выводов - в табл. 2. Большинство выводов микропроцессора КМ1801ВМ3 совпадает по назначению с выводами микропроцессора К1801ВМ2[*]. Рассмотрим подробнее функции несовпадающих выводов.

Таблица 1

Система команд микропроцессора КМ1801ВМ3

|

№ п/п |

Мнемоника |

Код |

Описание команды |

|---|---|---|---|

|

1 |

HALT |

000000 |

Останов |

|

2 |

WAIT |

000001 |

Ожидание |

|

3 |

RTI |

000002 |

Возврат из прерывания |

|

4 |

BPT |

000003 |

Командное прерывание для отладки |

|

5 |

IOT |

000004 |

Командное прерывание для ввода-вывода |

|

6 |

RESET |

000005 |

Сброс внешних устройств |

|

7 |

RTT |

000006 |

Возврат из прерывания |

|

8 |

JMP |

0001DD |

Безусловный переход |

|

9 |

RTS |

00020R |

Возврат из подпрограммы |

|

10 |

JSR |

004RDD |

Обращение к подпрограмме |

|

11 |

EMT |

104000 ... 104377 |

Командное прерывание для системных программ |

|

12 |

TRAP |

104400 ... 104777 |

Командное прерывание |

|

13 |

NOP |

000240 |

Нет операции |

|

14 |

CLC |

000241 |

Очистка С |

|

15 |

CLV |

000242 |

Очистка V |

|

16 |

CLZ |

000244 |

Очистка Z |

|

17 |

CLN |

000250 |

Очистка N |

|

18 |

SEC |

000261 |

Установка С |

|

19 |

SEV |

000262 |

Установка V |

|

20 |

SEZ |

000264 |

Установка Z |

|

21 |

SEN |

000270 |

Установка N |

|

22 |

SCC |

000277 |

Установка всех разрядов (N, Z, V, С). |

|

23 |

CCC |

000257 |

Очистка всех разрядов (N, Z, V, С) |

|

24 |

SWAB |

0003DD |

Перестановка байтов |

|

25 |

CLR (B) |

*050DD |

Очистка |

|

26 |

COM (B) |

*051DD |

Инвертирование |

|

27 |

INC (B) |

*052DD |

Прибавление единицы |

|

28 |

DEC (B) |

*053DD |

Вычитание единицы |

|

29 |

NEG (B) |

*054DD |

Изменение знака |

|

30 |

ADC (B) |

*055DD |

Прибавление переноса |

|

31 |

SBC (B) |

*056DD |

Вычитание переноса |

|

32 |

TST (B) |

*057DD |

Проверка |

|

33 |

ROR (B) |

*060DD |

Циклический сдвиг вправо |

|

34 |

ROL (B) |

*061DD |

Циклический сдвиг влево |

|

35 |

ASR (B) |

*062DD |

Арифметический сдвиг вправо |

|

36 |

ASL (B) |

*063DD |

Арифметический сдвиг влево |

|

37 |

MARK |

0064NN |

Восстановление указателя стека |

|

38 |

SXT |

0067DD |

Расширение знака |

|

39 |

MTPS |

1064SS |

Запись слова состояния программы |

|

40 |

MFPS |

1067DD |

Чтение слова состояния программы |

|

41 |

MOV (B) |

*1SSDD |

Пересылка |

|

42 |

CMP (B) |

*2SSDD |

Сравнение |

|

43 |

BIT (B) |

*3SSDD |

Проверка разрядов |

|

41 |

BIC (B) |

*4SSDD |

Очистка разрядов |

|

45 |

BIS (B) |

*5SSDD |

Логическое сложение |

|

46 |

XOR |

074RDD |

Исключающее ИЛИ |

|

47 |

ADD |

06SSDD |

Сложение |

|

48 |

SUB |

16SSDD |

Вычитание |

|

49 |

BR |

0004XX |

Ветвление безусловное |

|

50 |

BNE |

0010XX |

Ветвление, если не равно нулю |

|

51 |

BEQ |

0014XX |

Ветвление, если равно нулю |

|

52 |

BGE |

0020XX |

Ветвление, если больше или равно нулю |

|

53 |

BLT |

0024XX |

Ветвление, если меньше нуля |

|

54 |

BGT |

0030XX |

Ветвление, если больше нуля |

|

55 |

BLE |

0034XX |

Ветвление, если меньше или равно нулю |

|

56 |

SOB |

077RNN |

Вычитание единицы и ветвление |

|

57 |

BPL |

1000XX |

Ветвление, если плюс |

|

58 |

BMI |

1004XX |

Ветвление, если минус |

|

59 |

BHI |

1010XX |

Ветвление, если больше |

|

60 |

BLOS |

1014XX |

Ветвление, если меньше или равно |

|

61 |

BVC |

1020XX |

Ветвление, если нет арифметического переполнения |

|

62 |

BVC |

1024XX |

Ветвление, если арифметическое переполнение |

|

63 |

BHIS, BCC |

1030XX |

Ветвление, если больше или равно |

|

64 |

BLO, BCS |

1034XX |

Ветвление, если меньше |

|

65 |

MUL |

070RSS |

Умножение |

|

66 |

DIV |

071RSS |

Деление |

|

67 |

ASH |

072RSS |

Сдвиг на «N» разрядов одного слова |

|

68 |

ASHC |

073RSS |

Сдвиг на «N» разрядов двойного слова |

|

69 |

MFPD |

1065SS |

Засылка слова данных в стек текущей моды по адресу предварительной моды |

|

70 |

MFPI |

0065SS |

Засылка слова инструкции в стек текущей моды по адресу предварительной моды |

|

71 |

MTPD |

1066DD |

Засылка слова данных из стека текущей моды по адресу предварительной моды |

|

72 |

MTPI |

0066DD |

Засылка слова инструкции из стека текущей моды по адресу предварительной моды |

|

Примечание. |

DD - приёмник. SS - источник, R - регистр процессора. * - «0» для слова, «1» для байта, XX-смещение восьми разрядов. |

Таблица 2

Назначение выводов микропроцессора КМ1801ВМ3

|

Вывод |

Обозначение |

Назначение |

|---|---|---|

|

1 |

DIN |

Чтение данных |

|

2 |

DOUT |

Запись данных |

|

3 |

SYNC |

Обмен |

|

4 |

SSYNC |

Приём адреса |

|

5 |

RPLY |

Ответ |

|

6 |

DMG |

Предоставление прямого доступа |

|

7 |

SACK |

Подтверждение выборки |

|

8 |

DMR |

Требование прямого доступа |

|

9 |

|

|

|

10 ... 25 |

AD0 ... AD15 |

Совмещённая шина адресов и данных |

|

26 ... 31 |

A16 ... A21/NS |

Старшие разряды адреса |

|

32 |

0V |

Общий |

|

33 |

CLR |

Установка |

|

34 |

BS |

Внешнее устройство |

|

35 |

SEL |

Обращение к системной области |

|

36 |

TA |

Выдача адреса |

|

37 |

UMAP |

Преобразование адресов. Общая шина |

|

38 ... 42 |

OV |

Общий |

|

43 |

UCC |

Напряжение питания |

|

44 |

EVNT |

Запрос таймера |

|

45 |

ET |

Разрешение зависания |

|

46 |

ACLO |

Авария питания |

|

47 |

HLT |

Останов |

|

48 ... 51 |

IRQ3 ... IRQ0 |

Запросы на прерывание |

|

52 |

DCLO |

Авария питания |

|

53 |

FPPTRP |

Сигналы связи с процессором плавающей запятой |

|

54 |

FPPRD |

|

|

55 |

HLTM |

Пультовой режим |

|

56 |

DREADY |

Сигналы связи с процессором плавающей запятой |

|

57 |

FL |

|

|

58 |

FD |

|

|

59 |

WO |

Режим включения |

|

60 |

CLC |

Синхронизация |

|

61 |

LIN |

Сигнал связи с процессором плавающей запятой |

|

62 |

IAK |

Предоставление прерывания |

|

63 |

WTBT |

Запись/байт |

|

64 |

Ucc |

Напряжение питания |

Рис 2 Условное графическое изображение микросхемы КМ1801ВМ3

Группа выводов FPPTRP, FPPRD, LIN, FD, EL, DREADY позволяет организовать связь процессора плавающей запятой с микропроцессором и памятью. При установленном сигнале ЕТ в случае зависания системной магистрали через 128Т (Т-период тактовой частоты CLC) возникает прерывание, в противном случае прерывание не возникает. При переходе микропроцессора в пультовый режим устанавливается сигнал HLTM. Старшие разряды шины адреса А16...А20, A21/NS позволяют адресовать до 4М байт памяти. Вывод A21/NS имеет следующие назначения: выдача старшего разряда адреса в момент установления сигнала SYNC и признак чтения команды во время установленного сигнала DIN (для связи с процессором плавающей запятой). Сигнал BS вырабатывается при обращении к старшему банку системной памяти, сигнал SEL - при обращении к области программы пультового режима, сигнал ТА - в момент выдачи адреса в цикле чтения. Сигнал UMAP предназначен для управления дополнительной аппаратурой преобразования адресов «Общей шины».

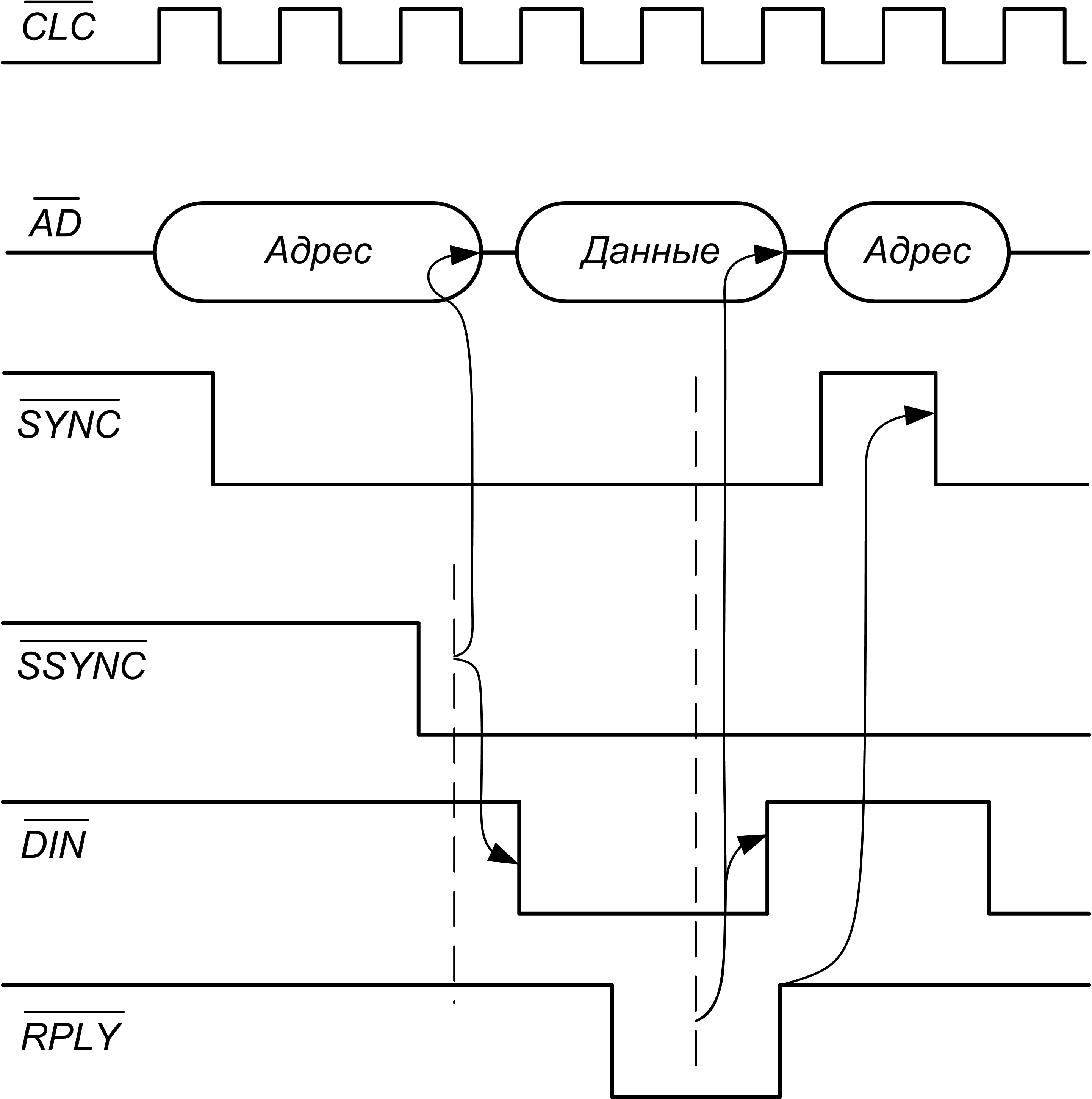

При обращении процессора к памяти или внешним устройствам возможны следующие виды обменов: чтение, запись, чтение-модификация-запись. Так как все обмены выполняются в соответствии со стандартным интерфейсом МПИ, то рассмотрим лишь особенности временных и логических связей сигналов системной магистрали микропроцессора КМ1801ВМ3.

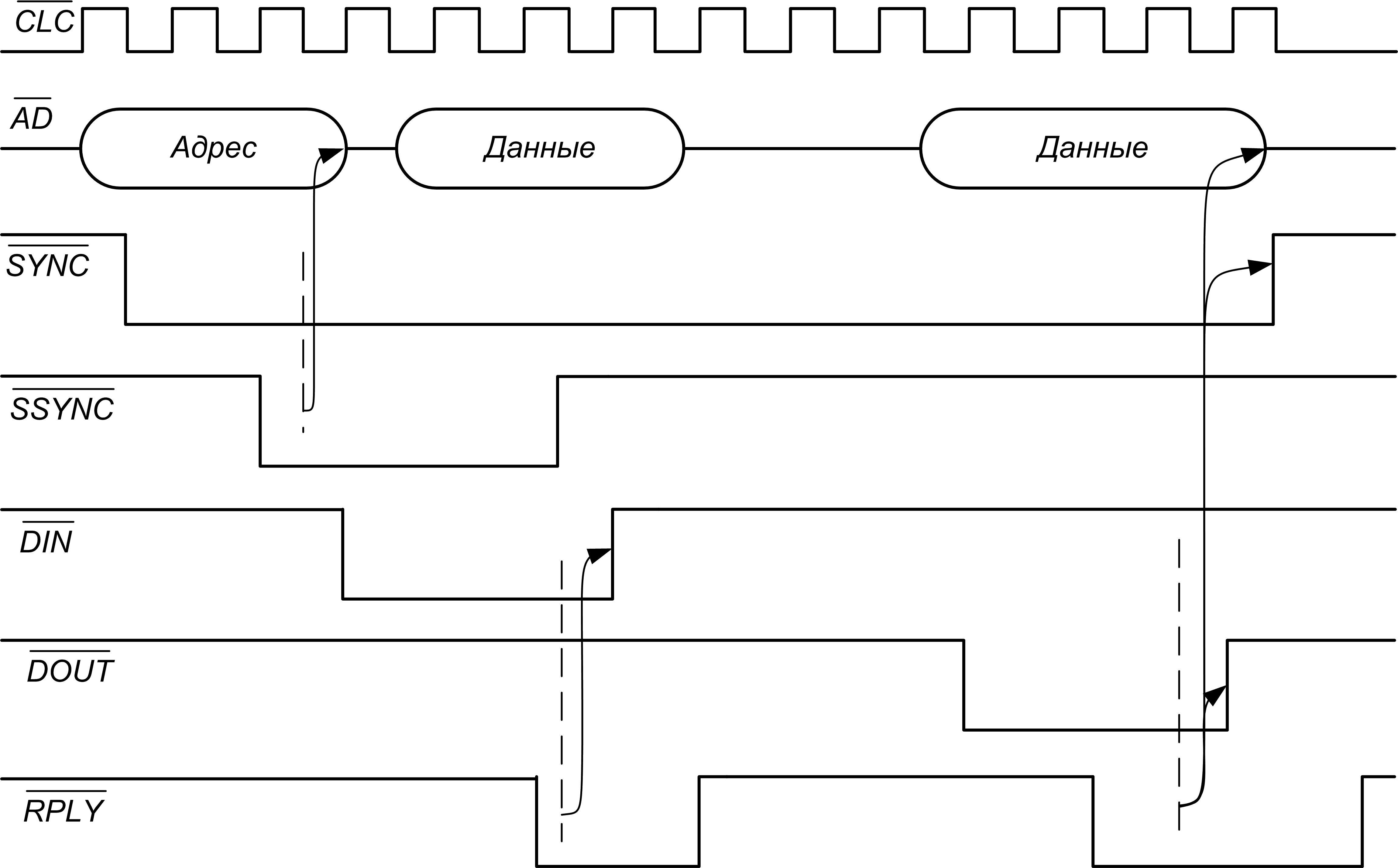

В цикле чтения (рис. 3) после выдачи адреса через 0,5Т выдаётся сигнал SYNC. Затем через 0,5Т после выполнения условия SYNC & & SSYNC & ↑CLC (где ↑CLC - момент переходя сигнала CLC из «0» в «1») адрес сбрасывается и выставляется сигнал DIN. Если в момент выдачи адреса сигнал SSYNC уже установлен, то сигнал DIN выставляется через 0,5Т после возникновения сигнала SYNC. При отсутствии сигнала SSYNC в течение 128Т после установления сигнала SYNC возникает прерывание Ошибка канала.

Рис. 3 Режим чтения

Данные с магистрали принимаются через 0,5Т после выполнения условия DIN & RPLY ↑CLC. Новый обмен (выдача адреса) начинается через 0,5Т после выполнения условия RPLY& SACK & DMR & ↑CLC.

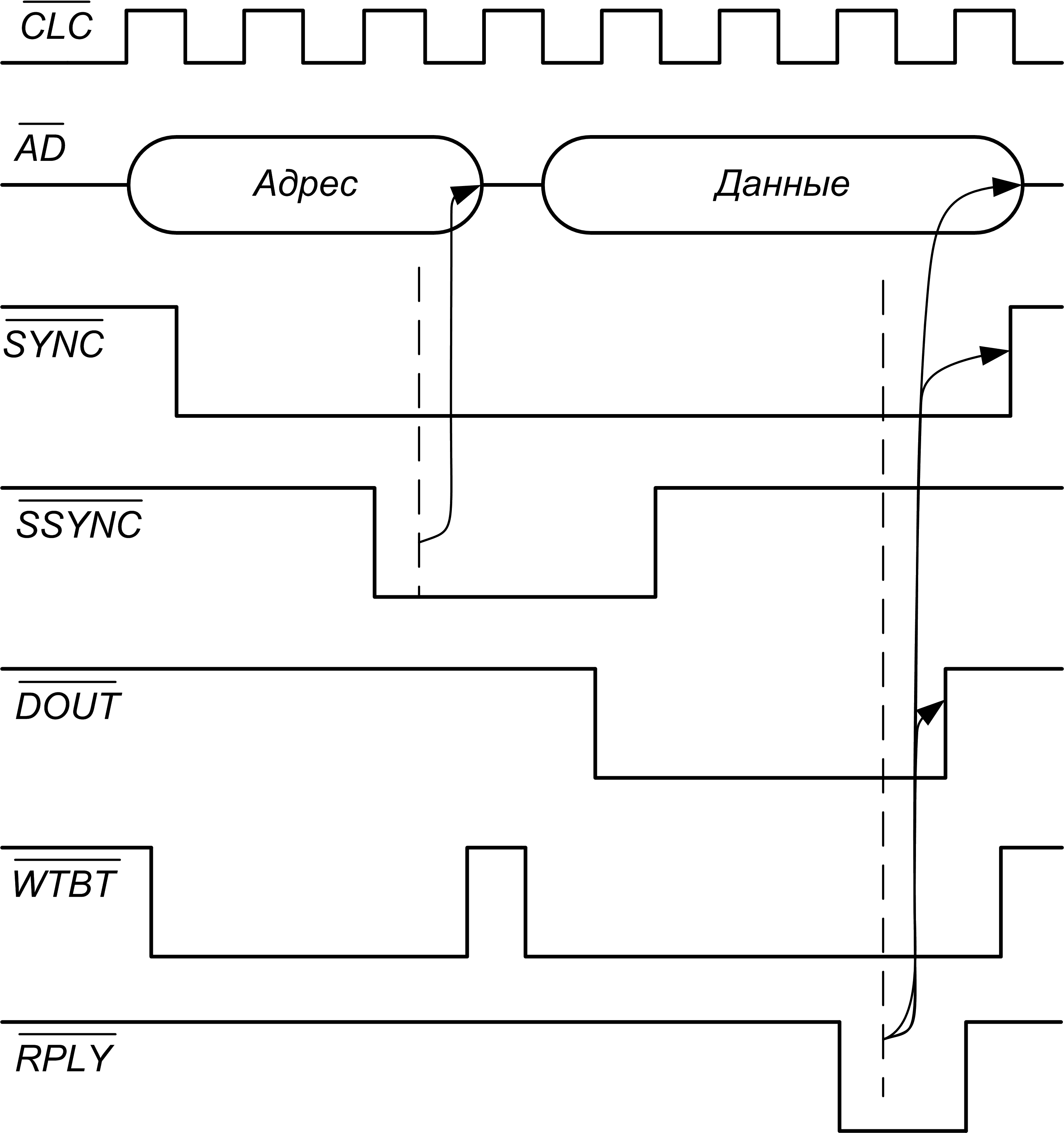

В цикле записи (рис. 4) выдача адреса осуществляется аналогично циклу чтения. Затем после выполнения условия SYNC & SSYNC & ↑CLC в готовности данных в операционном блоке данные выдаются на магистраль AD и через 0.5Т после этого устанавливается сигнал DOUT. Через 0.5Т после выполнения условия DOUT & RPLY & ↑CLC снимается сигнал DOUT ещё через 0,5Т - данные, ещё через 0,5Т - сигнал SYNC.

Рис. 4. Режим записи

Временная диаграмма цикла чтение - модификация - запись (рис. 5) в процессе считывания аналогична временной диаграмме чтения, а окончание обмена аналогично циклу записи. Минимальная задержка между первым моментом выполнения условия RPLY&↑CLC и выдачей сигнала DOUT равна τmin= 4,5Т.

Рис. 5. Режим чтения - модификации - записи

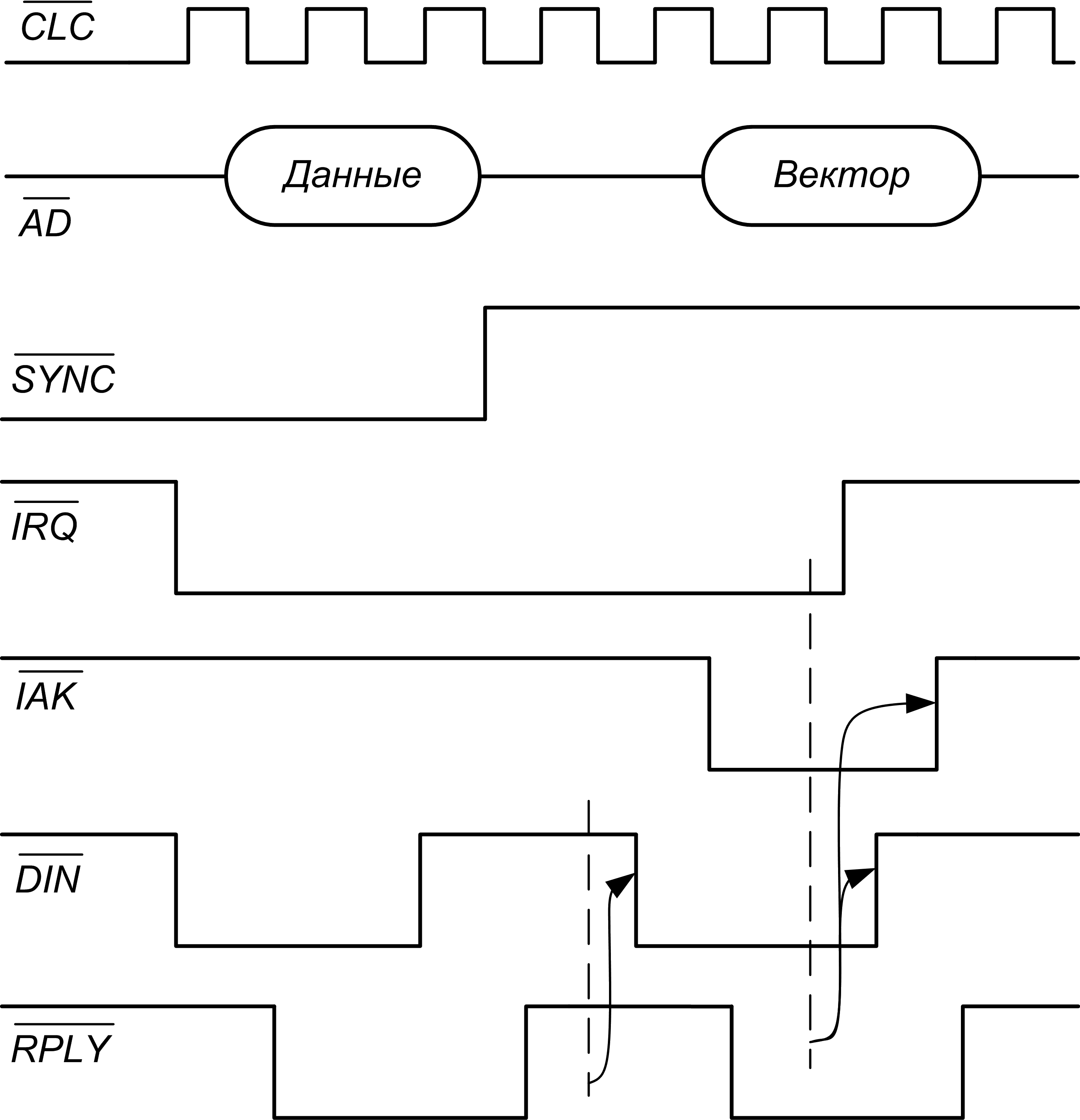

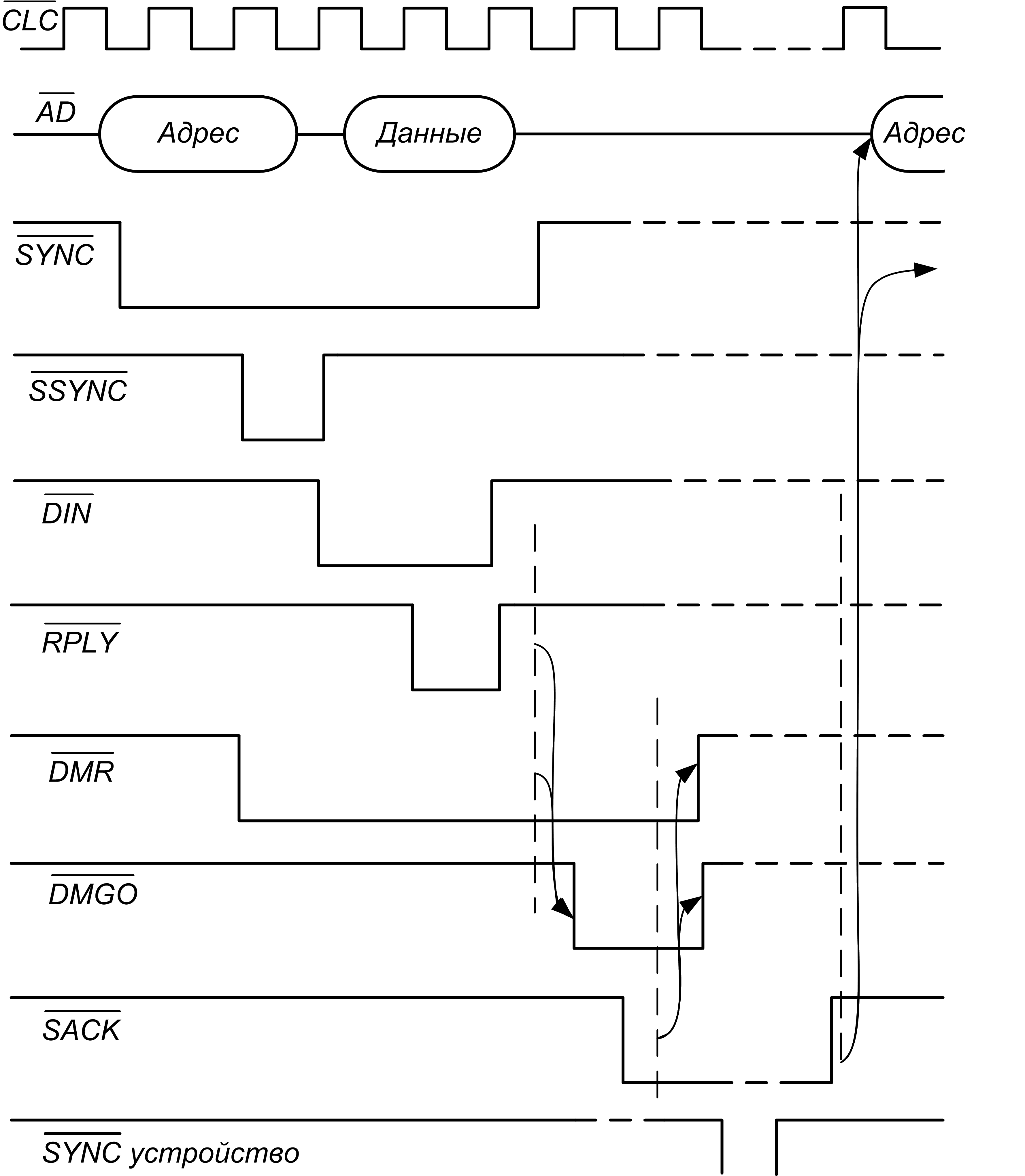

В случае возникновения одного из незамаскированных прерываний IRQ (3-0) и при отсутствии других более приоритетных прерываний процессор после завершения выполнения очередной команды переходит к процедуре обработки прерывания IRQ. При этом чтение вектора прерывания осуществляется при помощи специальной процедуры безадресного чтения по системной магистрали (рис. 6). В этом случае после завершения очередного обмена и освобождения магистрали, т. е. выполнения условия RPLY & SACK & DMR&↑CLC, через 2,5T выдаётся сигнал DIN и затем ещё через 0,5Т сигнал IAK. После выполнения условия DIN & RPLY & IAK &↑CLC через 0,5T снимается сигнал DIN и ещё через 0,5T сигнал IAK.

Рис. 6. Режим чтения вектора прерывания

Кроме процессора на системной магистрали активными устройствами могут быть устройства прямого доступа к памяти. Временная диаграмма захвата магистрали таким устройством показана на рис. 7. Здесь формирование сигнала DMGO происходит через 0,5Т после выполнения условия DMR & RPLY &↑CLC. При отсутствии в течение 128Т сигнала SACK после выставления сигнала DMGO последний снимается и арбитраж магистрали повторяется заново с учётом запросов процессора и устройств прямого доступа.

Рис. 7. Захват магистрали устройством прямого доступа

При включении питания после выработки сигналов DCLO и ACLO процессор переходит к одной из двух микропрограмм начального пуска в зависимости от состояния на входе WO:

- на входе WO - низкий уровень. Процессор загружает в слово состояния программы константу 3408, в регистр счётчика - адрес 1730008 и с него начинает выполнение программы;

- на входе WO - высокий уровень. Процессор загружает в слово состояния программы содержимое ячейки памяти с адресом 268, в счётчик содержимое ячейки памяти с адресом 248 и с него начинает выполнение программы.

Если при включении питания установлен сигнал HLT, то процессор переходит в пультовой режим. Расширение ёмкости адресуемой памяти осуществляется преобразованием 16-разрядного виртуального адреса в 18- или 22-разрядный физический адрес. Это преобразование осуществляется с помощью набора шестнадцати регистров адреса страницы (РАС) и шестнадцати регистров-описателей страницы (РОС).

Диспетчер памяти преобразует виртуальные адреса в физические суммированием виртуального значения со значением соответствующего РАС и производит проверку прав доступа в страницу. Функционально регистры РАС и РОС разделены на две группы. Первая обслуживает виртуальную машину ОС, вторая виртуальные машины пользователей. В режиме ОС возможно выполнение всего списка команд, включая команды HALT, RESET и команды, изменяющие приоритет процессора.

Для обеспечения эффективной работы алгоритмов смены страниц логика диспетчера памяти содержит для каждой страницы W-бит, указывающий, что в данную страницу сделана запись. При работе в режимах свопинга или оверлейном W-бит может использоваться для определения страниц, модифицированных пользователем.

Во время выполнения процессором текущей программы могут возникнуть условия прерывания (см. ниже).

|

Приоритет |

Источник прерывания |

|---|---|

|

Высший |

Команда HALT |

|

|

Ошибка нечётного адреса |

|

|

Ошибка диспетчера памяти |

|

|

Зависание системной магистрали |

|

|

Команды прерываний Т-бит |

|

|

Переполнение стека |

|

|

Авария источника питания |

|

|

Сигнал HLT |

|

|

EVNT (при условии ССП (7-5) ≤ 5) |

|

|

IRQ3 (ври условии ССП (7-5) ≤ 6) |

|

|

IRQ2 (при условии ССП (7-5) ≤ 5) |

|

|

IRQ1 (при условии ССП (7-5) ≤ 4) |

|

|

IRQ0 (при условии ССП (7-5) ≤ 3) |

|

Низший |

Выполнение очередной команды |

Прерывания, вызывающие немедленное прекращение выполнения команды и переход к микропрограмме перехода к программе обработки прерывания, возникают при ошибках системной магистрали диспетчера памяти, процессора плавающей запятой. Анализ прерываний, авария источника питания, сигнала HLT, EVNT, IRQ (3-0). переполнение стека в моде ОС производятся после завершения очередной команды в соответствии с приоритетом.

Переход к процедуре обработки прерывания включает в себя сохранение в стеке слова состояния программы и счётчика команд текущего процесса, формирование значения адреса вектора прерывания, по которому затем происходит загрузка новых значений, причём загрузка всегда ведётся из области памяти ОС. Особый случай представляет собой возникновение ошибки системной магистрали в ходе выполнения микропрограммы обработки прерывания - так называемая «двойная ошибка», когда процессор переходит в пультовой режим. В этот режим процессор может перейти и в результате выполнения команды HALT в моде ОС или возникновения внешнего сигнала ПЕТ и отсутствия в этот момент других более приоритетных прерываний. Пультовой режим реализуется программно, по в процессоре имеется его аппаратная поддержка. При обращении в память к программе HALT-моды процессор вырабатывает сигнал SEE, что позволяет не занимать под эту память адресного пространства ОЗУ. При работе в HALT-моде процессор использует в качестве указателя стека один из внутренних регистров - аккумуляторов. Это упрощает вход в HALT-моду и выход из неё. В диспетчер памяти введены четыре дополнительных регистра РАС для организации доступа к программе HALT-моды, к банку внешних устройств, а также ко всем 4М байтам в памяти. Значения трёх из этих регистров постоянны, а один доступен по чтению и записи по адресу 1725128.

В пультовом режиме существуют отличия в выполнении некоторых команд и обработке прерываний: нельзя использовать прерываний по командам MUL, DIV, ASH, ASHC, MTPD (I), MFPD (I). Ограничения обусловлены организацией регистра указателя стека в одном из внутренних регистров, а также тем, что выход из пультового режима осуществляется с помощью команд RTT и RTI, которые выполняются без учёта значения Т-бита. В этом режиме блокируются прерывания от диспетчера памяти путём загрузки в слово состояния программы значения 340. замаскированы прерывания EVNT, IRQ (3-0). В случае возникновения ошибки системной магистрали не происходит обычной процедуры обработки прерывания, а в регистр счётчика команд загружается значение 4 и процессор переходит к выполнению программы по этому адресу.

Для подключения к микропроцессору сопроцессора плавающей запятой в блоке микропрограммного управления выполняется фаза адресации команд арифметики с плавающей запятой, в блоке магистрали предусмотрена возможность организаций четырёх дополнительных типов обмена процессора плавающей запятой, введены дополнительные выводы.

Статья поступила 3 апреля 1986 г.

[*] Однокристальные микропроцессоры комплекта БИС серии К1801 / В.Л. Дшхунян, Ю.И. Борщенко, В.Р. Науменков и др. // Микропроцессорные средства и системы, 1984, № 4, с, 12-18.