УДК 681.323-181.48

В.Л. Дшхунян, Ю.И. Борщенко, В.Р. Науменков, А.А. Рыжов, Ю.В. Романец, И.А. Бурмистров, Е.М. Соловьев

ОДНОКРИСТАЛЬНЫЕ МИКРОПРОЦЕССОРЫ КОМПЛЕКТА БИС СЕРИИ К1801

Однокристальные микропроцессоры (ОМП) К1801ВМ1 и КМ1801ВМ2 являются основой магистрально-модульного микропроцессорного комплекта БИС серий К1801/К1809 [1,2], обеспечивающего возможность построения широкого класса микро-ЭВМ, различных микроконтроллеров и управляющих микропроцессорных систем.

Однокристальный микропроцессор К1801ВМ1

Микросхема К1801ВМ1 является однокристальным 16-разрядным микропроцессором, предназначенным для обработки цифровой информации в системах управления технологическими процессами, контрольно-измерительной аппаратуре и системах связи, а также решения в составе ЭВМ инженерно-технических и экономических задач.

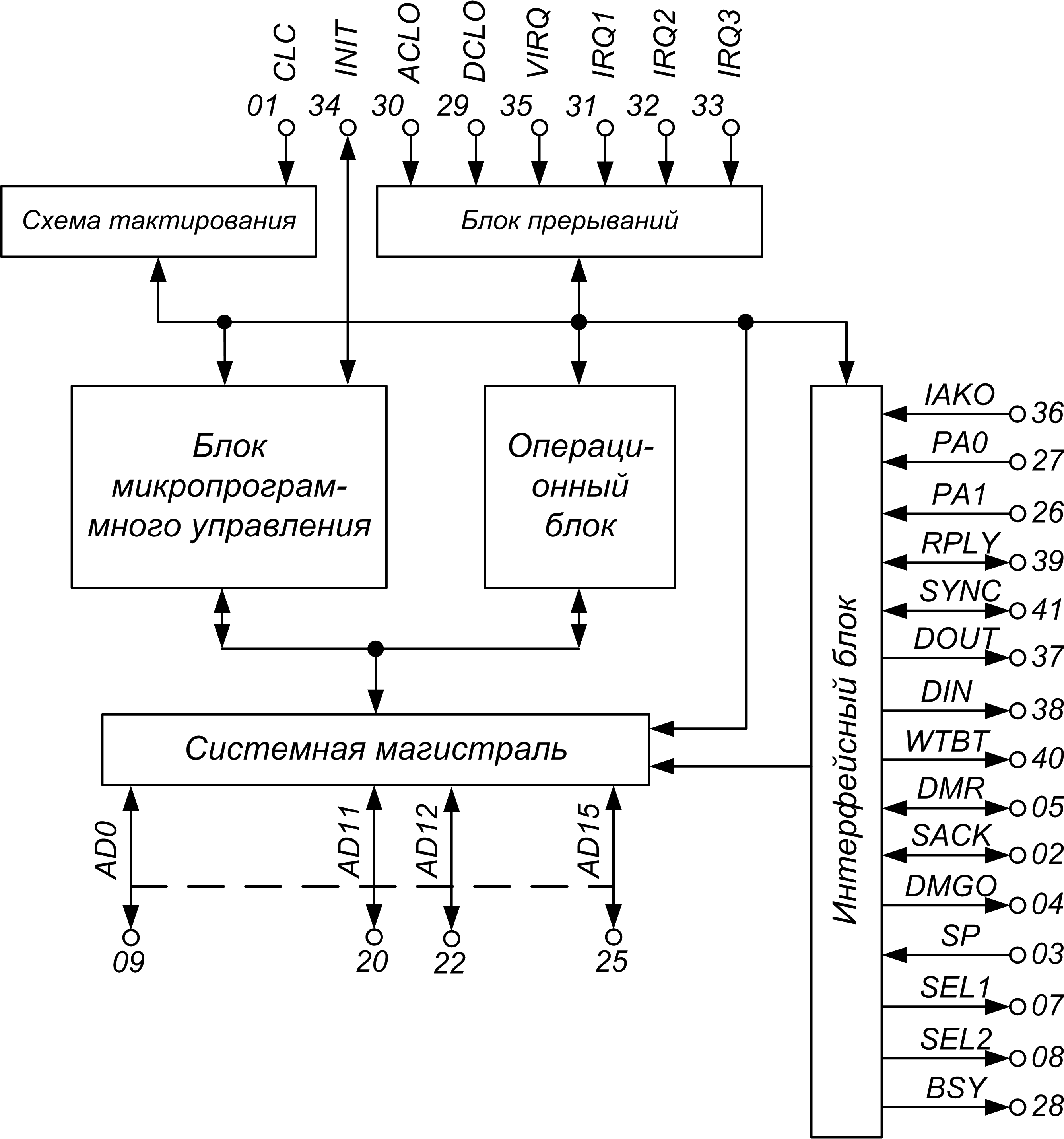

Рис. 1. Структурная организация процессора К1801ВМ1

Микропроцессор содержит следующие основные функциональные блоки, объединённые информационно-управляющими связями (рис. 1):

- 16-разрядный операционный блок, выполняющий операции формирования адресов команд и операндов, логические и арифметические операции, хранение операндов и результатов;

- блок микропрограммного управления, вырабатывающий последовательность микрокоманд на основе кода принятой команды. Выполнен на базе программируемой логической матрицы (ПЛМ), содержащей 250 логических произведений. В ПЛМ закодирован полный набор микрокоманд для всех типов команд. Программирование ПЛМ производится на этапе изготовления микросхемы с помощью одного фотошаблона;

- блок прерываний, организующий приоритетную систему прерываний. Выполняет приём и предварительную обработку внешних и внутренних запросов на прерывание вычислительного процесса;

- интерфейсный блок, отвечающий за обмен информацией между ОМП и устройствами, расположенными на системной магистрали. Осуществляет арбитраж при операциях прямого доступа к памяти, формирует последовательность управляющих сигналов;

- блок системной магистрали, связывающий внутреннюю магистраль ОМП с внешней. Управляет усилителями приёма и выдачи информации на совмещённые выводы адресов и данных;

- схема тактирования, обеспечивающая синхронизацию внутренних блоков ОМП.

Ниже приведены основные технические характеристики ОМП.

Технические характеристики микропроцессора К1801ВМ1

|

Представление чисел |

дополнительный код с фиксированной запятой |

|

Система команд |

безадресная, одноадресная, двухадресная |

|

Виды адресации |

регистровая, косвенно-регистровая, автоинкрементная, косвенно-автоинкрементная автодекрементная, косвенно-автодекрементная, индексная, косвенно-индексная |

|

Число регистров общего назначения (РОН) |

8 |

|

Число уровней прерываний |

4 |

|

Системная магистраль |

типа МПИ |

|

Адресное пространство, Кбайт |

64 |

|

Тактовая частота, МГц |

до 5 |

|

Максимальное быстродействие при выполнении регистровых операций, операций/с |

до 500 тыс. |

|

Потребляемая мощность, Вт. |

до 1 |

|

Напряжение питания, В |

+5±5% |

|

Уровни логических сигналов, В: |

|

|

«Лог. 0» (активный уровень) |

менее 0,5 |

|

«Лог. 1» |

более 2,4 |

|

Нагрузочная способность по току, мА |

3,2 |

|

Ёмкость нагрузки, пФ |

до 100 |

|

Технология изготовления |

N-МОП |

|

Конструкция |

42-выводной планарный металлокерамический корпус |

Система команд (табл. 1), реализованная в ПЛМ блока микропропрограммного управления ОМП соответствует микро-ЭВМ «Электроника 60».

|

№№ пп. |

Обозначение |

Код |

Наименование |

|---|---|---|---|

|

1 |

HALT |

000000 |

Останов |

|

2 |

WAIT |

000001 |

Ожидание |

|

3 |

RTI |

000002 |

Возврат из прерывания |

|

4 |

BPT |

000003 |

Командное прерывание для отладки |

|

5 |

IOT |

000004 |

Командное прерывание для ввода-вывода |

|

6 |

RESET |

000005 |

Сброс внешних устройств |

|

7 |

RTT |

000006 |

Возврат из прерывания |

|

8 |

JMP |

0001DD |

Безусловный переход |

|

9 |

RTS |

00020R |

Возврат из подпрограммы |

|

10 |

JSR |

004RDD |

Обращение к подпрограмме |

|

11 |

EMT |

104000 ... 104377 |

Командное прерывание для системных программ |

|

12 |

TRAP |

104400 ... 104777 |

Командное прерывание |

|

13 |

NOP |

000240 |

Нет операции |

|

14 |

CLC |

000241 |

Очистка С |

|

15 |

CLV |

000242 |

Очистка V |

|

16 |

CLZ |

000244 |

Очистка Z |

|

17 |

CLN |

000250 |

Очистка N |

|

18 |

SEC |

000261 |

Установка С |

|

19 |

SEV |

000262 |

Установка V |

|

20 |

SEZ |

000264 |

Установка Z |

|

21 |

SEN |

000270 |

Установка N |

|

22 |

SCC |

000277 |

Установка всех разрядов (N, Z, V, С) |

|

23 |

CCC |

000257 |

Очистка всех разрядов (N, Z, V, С) |

|

24 |

SWAB |

0003DD |

Перестановка байтов |

|

25 |

CLR(B) |

*050DD |

Очистка |

|

26 |

COM(B) |

*051DD |

Инвертирование |

|

27 |

INC(B) |

*052DD |

Прибавление единицы |

|

28 |

DEC(B) |

*053DD |

Вычитание единицы |

|

29 |

NEG(B) |

*054DD |

Изменение знака |

|

30 |

ADC(B) |

*055DD |

Прибавление переноса |

|

31 |

SBC(B) |

*056DD |

Вычитание переноса |

|

32 |

TST(B) |

*057DD |

Проверка |

|

33 |

ROR(B) |

*060DD |

Циклический сдвиг вправо |

|

34 |

ROL(B) |

*061DD |

Циклический сдвиг влево |

|

35 |

ASR(B) |

*062DD |

Арифметический сдвиг вправо |

|

36 |

ASL(B) |

*063DD |

Арифметический сдвиг влево |

|

37 |

MAPK |

0064NN |

Восстановление указателя стека |

|

38 |

SXT |

0067DD |

Расширение знака |

|

39 |

MTPS |

1064SS |

Запись слова состояния процессора |

|

40 |

MFPS |

1067DD |

Чтение слова состояния процессора |

|

41 |

MOV(B) |

*1SSDD |

Пересылка |

|

42 |

CMP(B) |

*2SSDD |

Сравнение |

|

43 |

BIT(B) |

*3SSDD |

Проверка разрядов |

|

44 |

BIC(B) |

*4SSDD |

Очистка разрядов |

|

45 |

BIS(B) |

*5SSDD |

Логическое сложение |

|

46 |

XOR |

074RDD |

Исключающее «или» |

|

47 |

ADD |

06SSDD |

Сложение |

|

48 |

SUB |

16SSDD |

Вычитание |

|

49 |

BR |

0004XXX |

Ветвление безусловное |

|

50 |

BNE |

0010XXX |

Ветвление, если не равно (нулю) |

|

51 |

BEQ |

0014XXX |

Ветвление, если равно (нулю) |

|

52 |

BGE |

0020XXX |

Ветвление, если больше и равно (нулю) |

|

53 |

BLT |

0024XXX |

Ветвление, если меньше (нуля) |

|

54 |

BGT |

0030XXX |

Ветвление, если больше (нуля) |

|

55 |

BLE |

0034XXX |

Ветвление, если меньше или равно (нулю) |

|

56 |

SOB |

077RNN |

Вычитание единицы и ветвление |

|

57 |

BPL |

1000XXX |

Ветвление, если плюс |

|

58 |

BMI |

1004XXX |

Ветвление, если минус |

|

59 |

BHI |

1010XXX |

Ветвление, если больше |

|

60 |

BLOS |

1014XXX |

Ветвление, если меньше или равно |

|

61 |

BVC |

1020XXX |

Ветвление, если нет арифметического переполнения |

|

62 |

BVS |

1024XXX |

Ветвление, если арифметическое переполнение |

|

63 |

BHIS, BCC |

1030XXX |

Ветвление, если больше или равно |

|

64 |

BLO, BCS |

1034XXX |

Ветвление, если меньше |

|

Примечание: |

В - байтовые команды; SS - поле адресации операнда источника; DD - поле адресации операнда приёмника; NN - смещение (6 разрядов); XXX - смещение (8 разрядов); R- регистр общего назначения (РОН); * - имеет значение: 0 - для команд с операцией над словами; 1-для команд с операцией над байтами. |

Помимо перечисленных команд ОМП имеет в своём составе специальные команды, предназначенные для работы с системным ПЗУ К1801РЕ1.

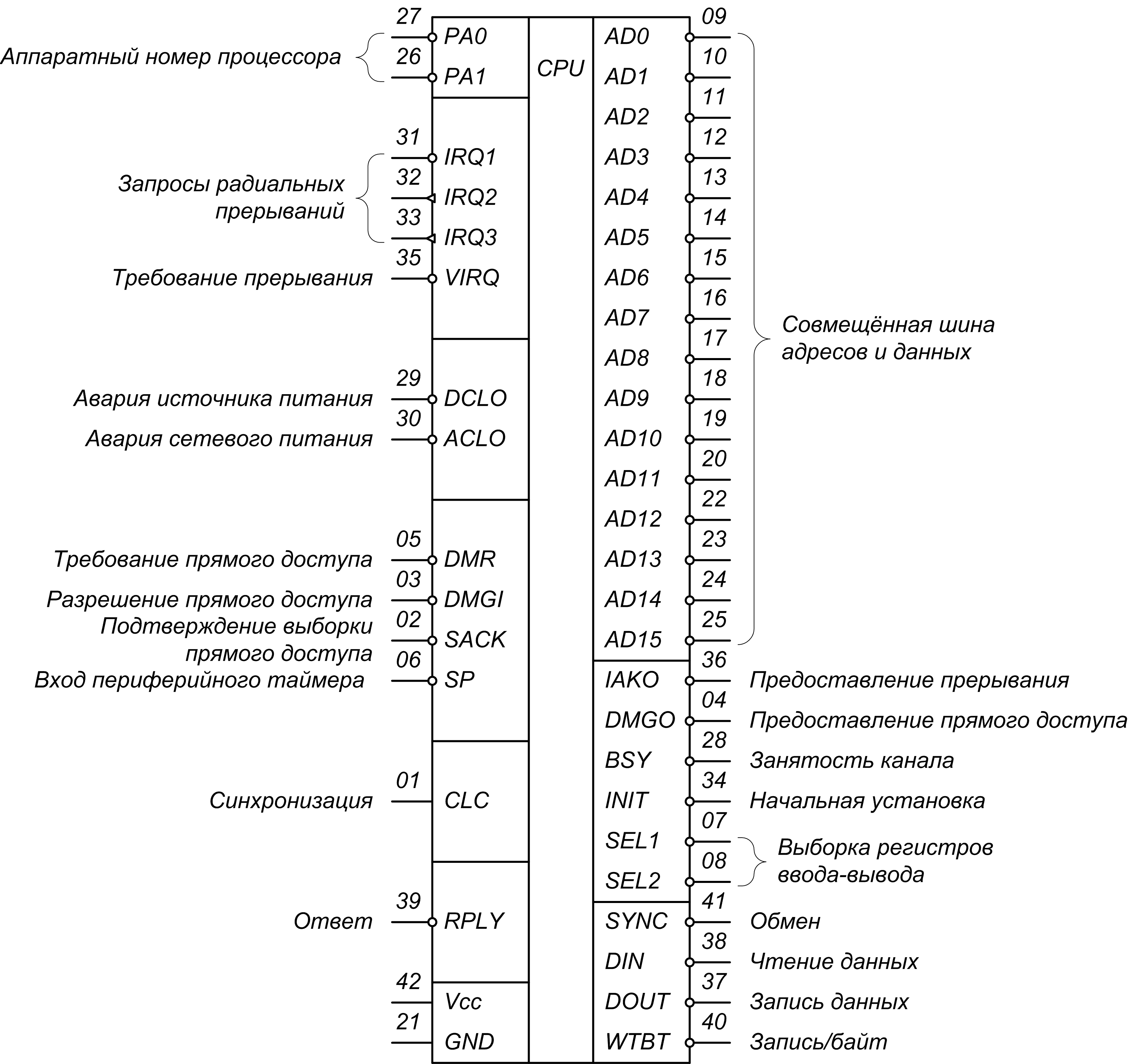

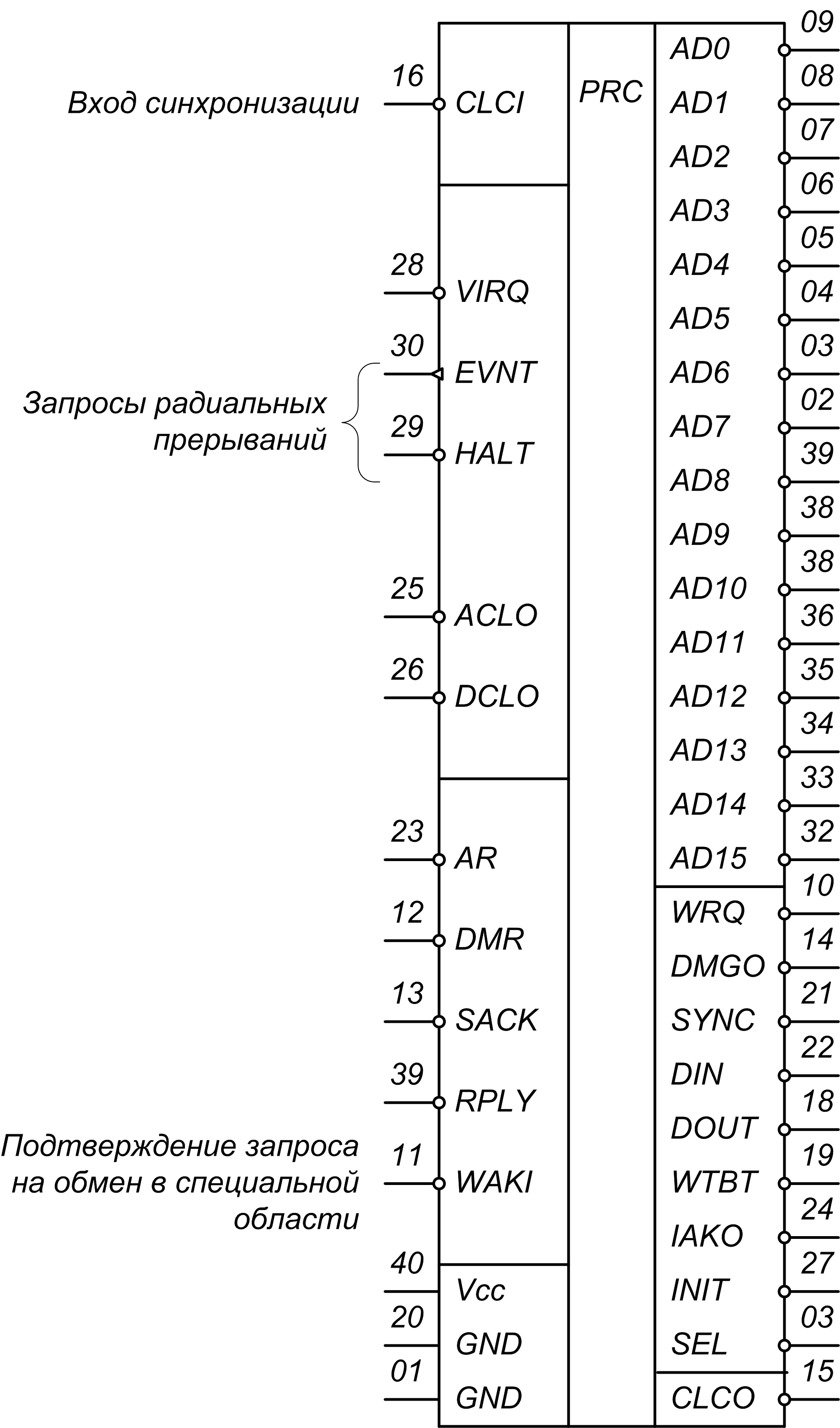

Условно-графическое обозначение микросхемы ОМП и наименование выводов приведены на рис. 2. Сигналы AD0...AD15 определяют адреса и данные, которые передаются несовмещённой системной магистрали. Передача адресов и данных по одним и тем же выводам обеспечивается разделением во времени.

Рис. 2. Условное графическое обозначение микросхемы К1801ВМ1

Группа сигналов SYNC, DIN, DOUT, WTBT, RPLY управляет передачей информации по системной магистрали. Сигнал SYNC, вырабатываемый процессором, означает, что адрес находится на выводах системной магистрали. Этот сигнал сохраняет активный уровень до окончания текущего обмена информацией.

Сигнал RPLY означает, что данные приняты или установлены на информационных выводах. Этот сигнал вырабатывается пассивным устройством в ответ на сигналы DIN и DOUT. Сигнал DIN предназначен для организации двух процедур обмена информацией по магистрали:

- ввода данных - ОМП вырабатывает DIN во время действия сигнала SYNC, когда он готов принять данные от пассивного устройства;

- ввода адреса вектора прерывания - сигнал DIN вырабатывается совместно с сигналом IAKO при пассивном уровне сигнала SYNC.

Сигнал DOUT означает, что данные, выдаваемые ОМП, установлены на выводах системной магистрали.

Сигнал WTBT предназначен для организации двух процедур обмена информацией:

- вырабатывается в адресной части цикла для указания о том, что далее следует вывод данных (слова или байта);

- формируется при выводе данных из ОМП для указания о выводе байта.

Сигнал VIRQ вырабатывается внешним устройством для информирования ОМП о том, что оно готово передавать адрес вектора прерывания. В ответ на этот сигнал, если прерывание разрешено, ОМП вырабатывает сигналы DIN и IAKO.

Сигнал IRQ1 определяет положение внешнего переключателя «Программа - пульт». Низкий уровень этого сигнала означает, что переключатель находится в положении «Пульт». Этот сигнал переводит ОМП в состояние, аналогичное состоянию после выполнения команды HALT.

Сигналы IRQ2 и IRQ3 вызывают прерывание программы, выполняемой процессором, по фиксированным адресам 000100(8) и 000270(8) соответственно. Прерывание происходит при переходе сигналов из высокого уровня в низкий.

Сигнал предоставления прерываний IAKO процессор вырабатывает в ответ на внешний сигнал VIRQ. Этот сигнал является выходным для ОМП и входным для первого устройства, подключённого к системной магистрали (электрически ближе расположенного к ОМП, и, следовательно, имеющего более высокий приоритет). Если это устройство не требовало прерываний (не устанавливало сигнал VIRQ), то оно транслирует сигнал IAKO к следующему устройству. Устройство, требующее прерывание ОМП, запретит распространение этого сигнала. Сигнал IAKO, последовательно проходя через все устройства, обеспечивает их поочерёдный опрос и различный приоритет обслуживания.

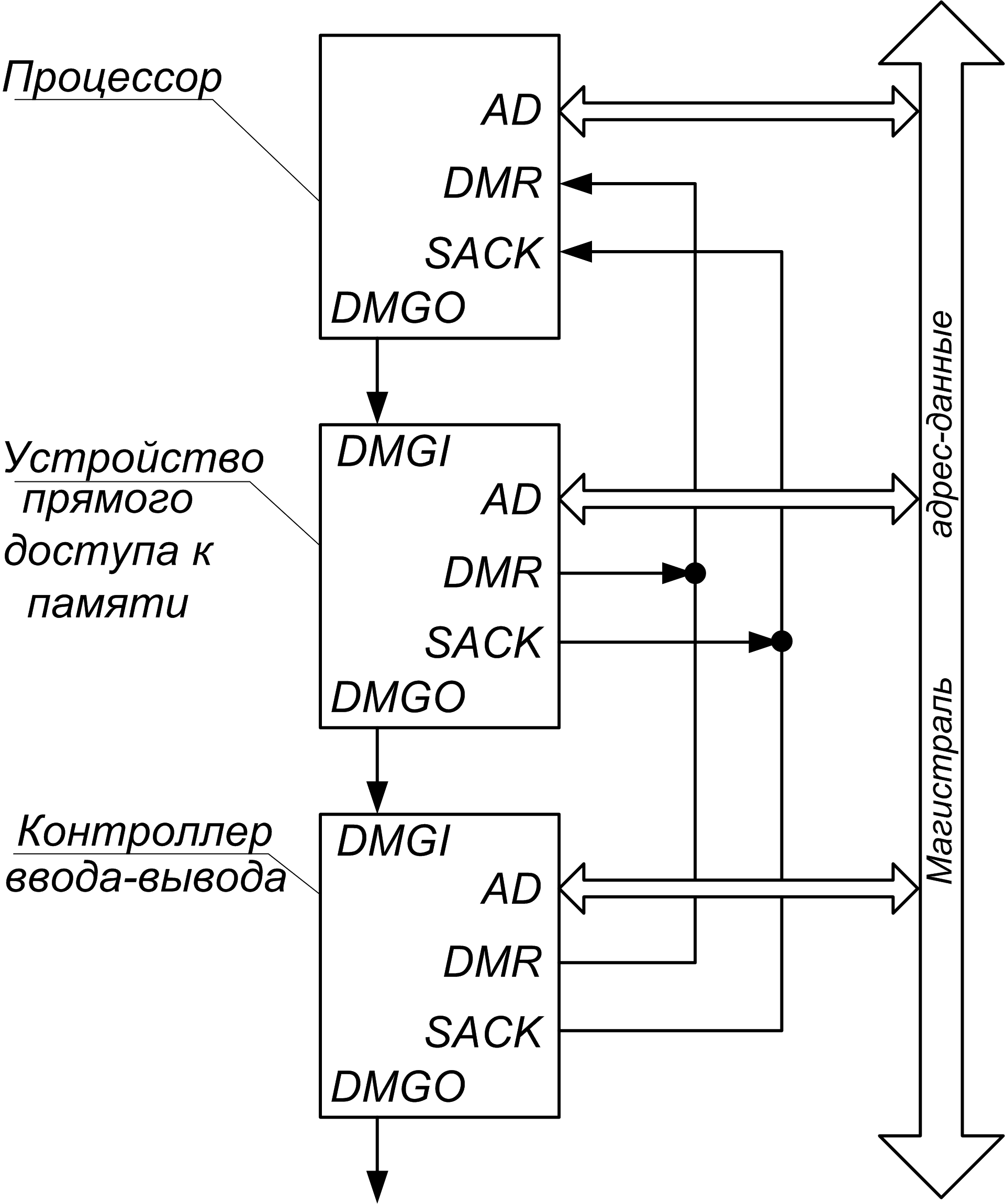

Сигнал DMR вырабатывает внешнее активное устройство, требующее передачи ему системной магистрали. Сигнал DMGO процессор устанавливает в ответ на внешний сигнал DMR. Этот сигнал последовательно проходит через внешние устройства и предоставляет системную магистраль устройству с наивысшим приоритетом, запросившему прямой доступ к памяти. Это устройство прекращает трансляцию сигнала DMGO и устанавливает сигнал SACK, который вырабатывается устройством прямого доступа к памяти (ПДП) в ответ на сигнал DMGO. Сигнал SACK означает, что устройство ПДП может производить обмен данными, используя стандартные циклы обращения к системной магистрали.

Сигнал занятости магистрали BSY предназначен для управлений устройствами умощнения магистрали. Низкий уровень этого сигнала означает, что ОМП начинает обмен по магистрали. Переход сигнала из низкого уровня в высокий означает окончание обмена.

Сигнал аварии источника питаний DCLO вызывает установку ОМП в исходное состояние и появление сигнала INIT. Сигнал аварии сетевого питания ACLO означает переход ОМП на обработку прерывания по сбою питания. Высокий уровень этого сигнала свидетельствует о том, что сетевое напряжение питания нормально.

При появлении одного из сигналов обращения к внешним регистрам расширения ввода-вывода SEL1, SEL2 адрес на выводах системной магистрали соответствует адресу одного из внешних регистров расширения ввода-вывода. Сигнал SEL1 устанавливается при обращении по фиксированному адресу 177716(8), сигнал SEL2 - по адресу 177714(8).

Совместно с сигналами DIN или DOUT происходит соответственно ввод данных в ОМП из регистров или вывод из ОМП на регистры. Установка сигнала RPLY от регистров расширения ввода-вывода не требуется. По длительности сигналы SEL1 и SEL2 совпадают с сигналом BSY.

Сигнал INIT является ответом ОМП на сигнал DCLO. Его используют для установки периферийной части системы в исходное состояние. При вводе этого сигнала в ОМП происходит сброс триггеров запроса радиальных прерываний и блокирования сигнала DMR.

Системная магистраль позволяет адресовать 64 Кбайта. Верхние 8 Кбайт адресного пространства резервируются для управления периферийными устройствами и регистрами данных. Магистраль позволяет организовать канал обмена информацией, аналогичный каналу микро-ЭВМ «Электроника 60», в котором связь между двумя устройствами осуществляется по принципу «активный-пассивный».

Активное устройство управляет прохождением информации по системной магистрали, разрешает прерывания, обеспечивает предоставление прямого доступа к памяти. Пассивное устройство передаёт информацию только под управлением активного устройства.

При обращении процессора к памяти или внешним устройствам возможны следующие виды обменов (циклов) информацией по системной магистрали: Ввод (Чтение), Вывод (Запись), Ввод-пауза-вывод (Чтение- модификация-запись).

Цикл Ввод-пауза-вывод включает ввод данных, выполнение арифметическо-логических операций и вывод результата без повторения передачи адреса, т.е. результат записывается по адресу последнего выбранного операнда.

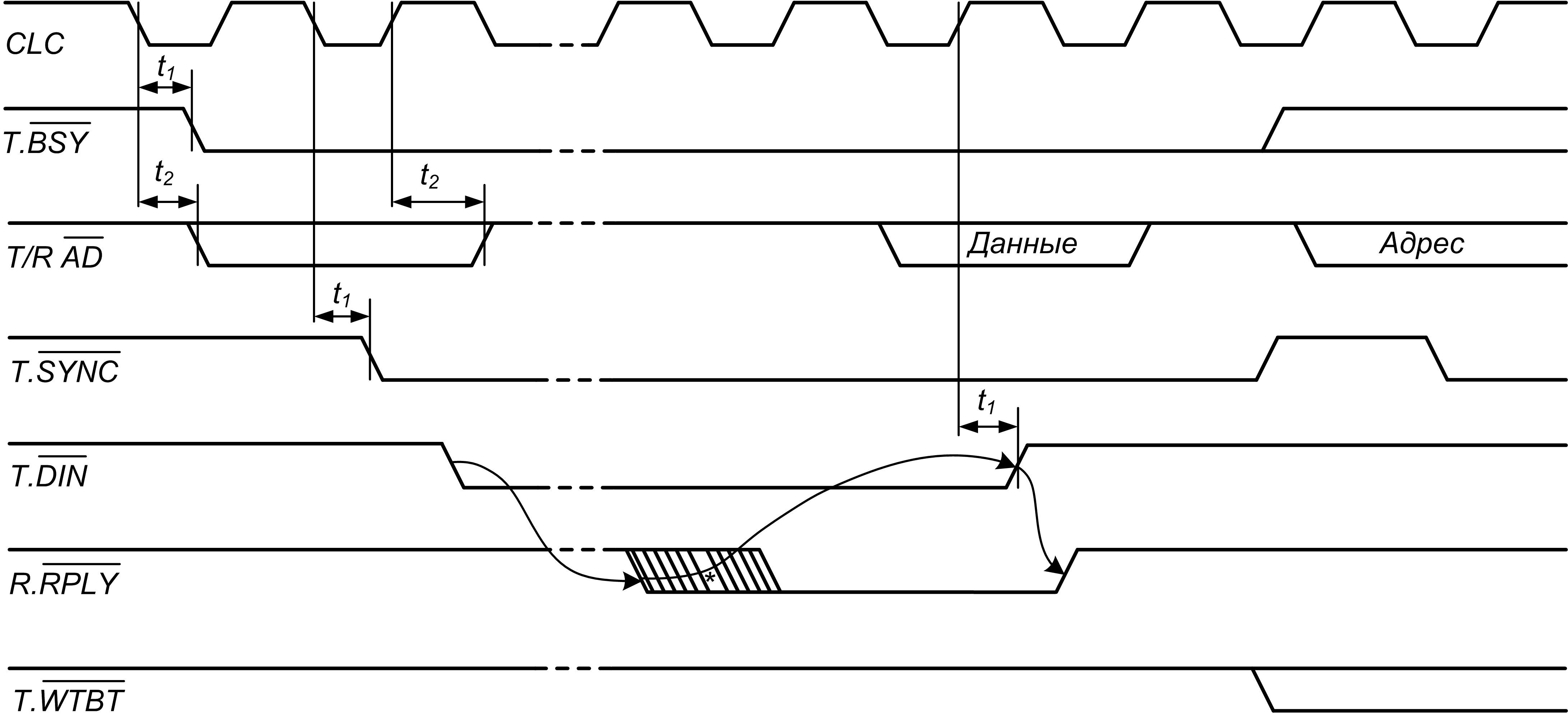

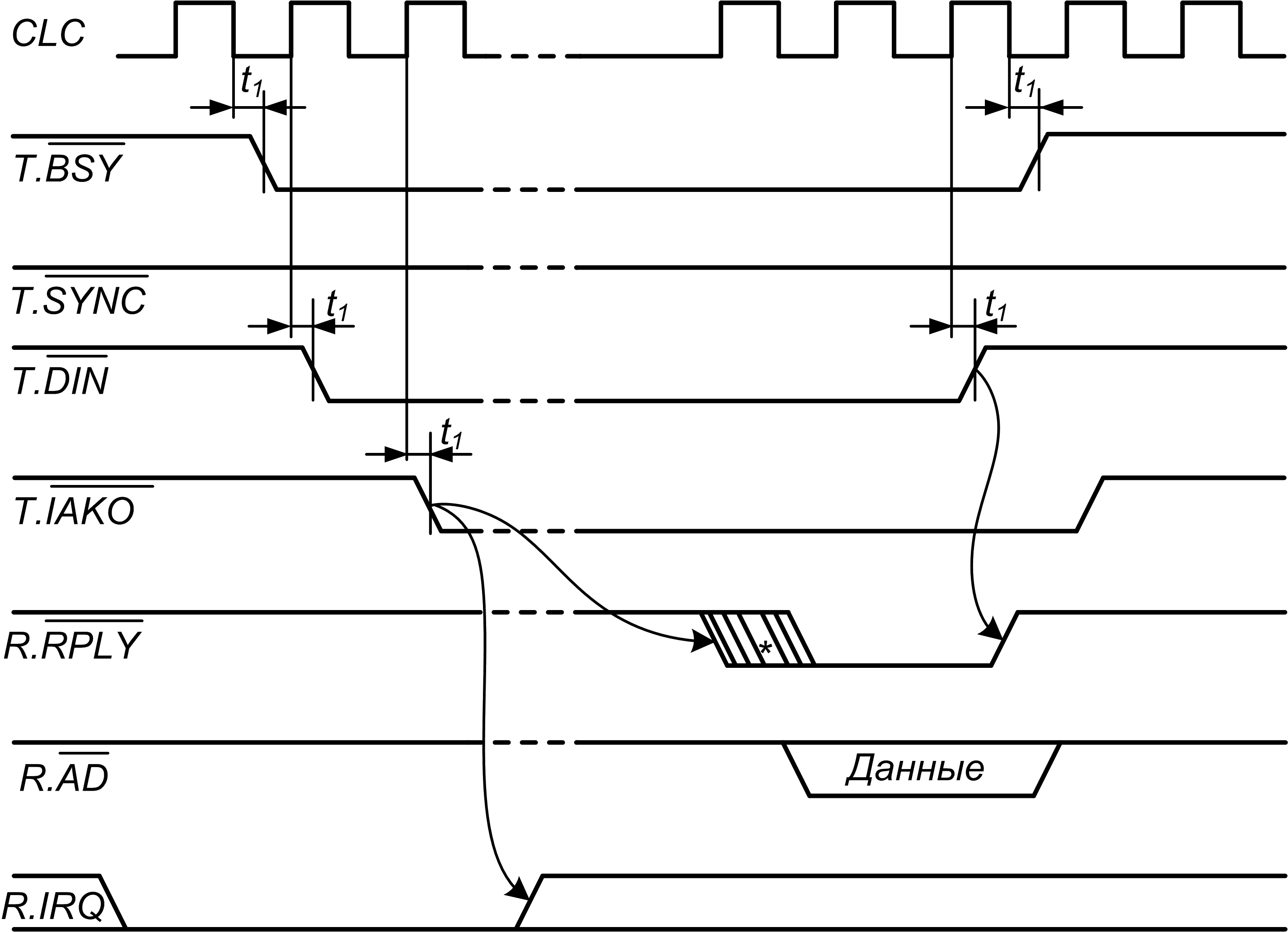

Ниже иллюстрируются некоторые виды обмена информацией по системной магистрали. При выполнении цикла Ввод данные передаются от пассивного устройства к активному. Временная диаграмма цикла приведена на рис. 3. Черта над обозначением сигнала указывает, что активным уровнем является низкий уровень сигнала.

Рис. 3. Временная диаграмма цикла Ввод (Чтение) информации по параметрам: Т - передатчик; R - приёмник; t1 =40...70 нс; t2 = 50...80 нс; * - область прихода сигнала RPLY, для которой соблюдается приведённая диаграмма

Порядок выполнения операций следующий:

- процессор на выводах системной магистрали устанавливает адрес и выдаёт сигнал BSY;

- синхронно с выдачей и снятием адреса ОМП устанавливает и снимает сигнал синхронизации SYNC, по которому происходит запоминание адреса пассивным устройством;

- после установки сигнала SYNC ОМП снимает адрес, устанавливает сигнал DIN и ожидает поступления сигнала RPLY от пассивного устройства. Если в течение 64 тактов частоты синхронизации сигнал RPLY не появился, ОМП переходит к обслуживанию внутреннего прерывания по ошибке обращения к системной магистрали;

- после приёма сигнала RPLY ОМП принимает данные от пассивного устройства и снимает сигнал DIN;

- после снятия сигнала DIN пассивное устройство снимает сигнал RPLY, завершая операцию передачи данных;

- после снятия сигнала RPLY пассивным устройством ОМП снимает сигналы SYNC и BSY;

- если системная магистраль не предоставляется устройству ПДП, то процессор сразу после снятия сигнала SYNC может начать новый цикл обращения к магистрали. В этом случае сигнал BSY не снимается. Во время цикла Ввод сигнал WTBT не вырабатывается.

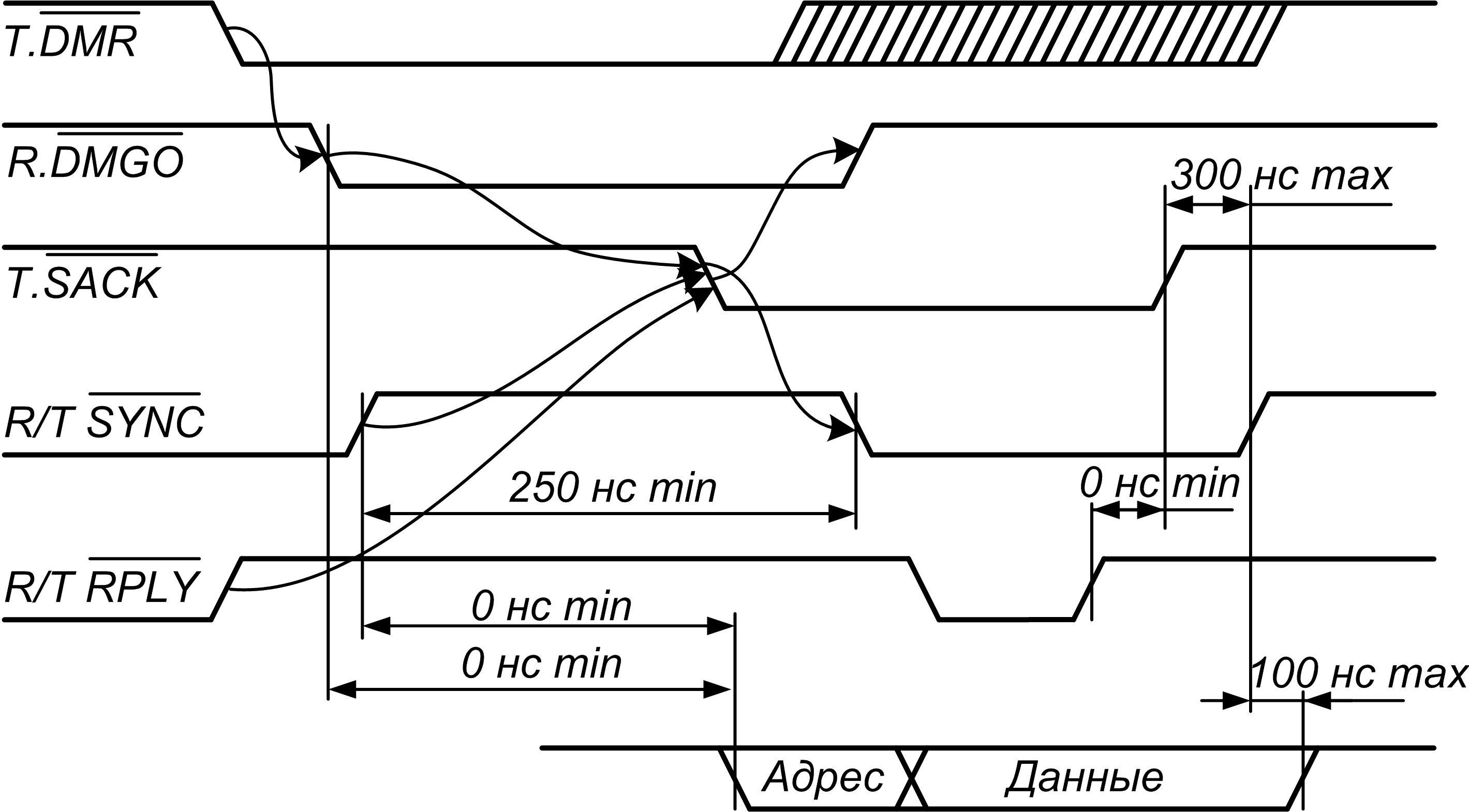

Кроме ОМП, активным устройством на системной магистрали может быть устройство ПДП, которое в режиме ПДП выполняет адресацию, синхронизацию, вырабатывает управляющие сигналы для организации стандартных циклов обращения к системной магистрали без вмешательства ОМП. Временная диаграмма ПДП представлена на рис. 4. Устройство ПДП устанавливает сигнал DMR, в ответ на который ОМП формирует сигнал DMGO, затем, получив сигнал DMGO, вырабатывает сигнал SACK, и снимает сигнал DMR. ОМП снимает сигнал DMGO и ожидает завершения операции ПДП. Устройство ПДП начинает выполнять циклы передачи данных, аналогичные циклам Ввод, Вывод или Ввод-пауза-вывод. После окончания обмена данными устройство ПДП снимает сигнал SACK, возвращая управление магистралью процессору.

Рис. 4. Временная диаграмма цикла ПДП

Регистры общего назначения (РОН) используются в качестве индексных и накопительных, регистров автоинкрементной и автодекрементной адресаций. Среди восьми РОН два регистра R6 и R7 имеют специальное назначение: R6 используется в качестве указателя стека и содержит адрес последней ячейки стека; R7 является счётчиком команд (СК) и содержит адрес очередной выполняемой команды.

Кроме РОН, программно доступным регистром является регистр состояния процессора (РСП), содержащий информацию о текущем приоритете ОМП, значения кодов условий ветвлений программы, состояние «Т-бита», используемого при отладке программы и вызывающего её прерывание.

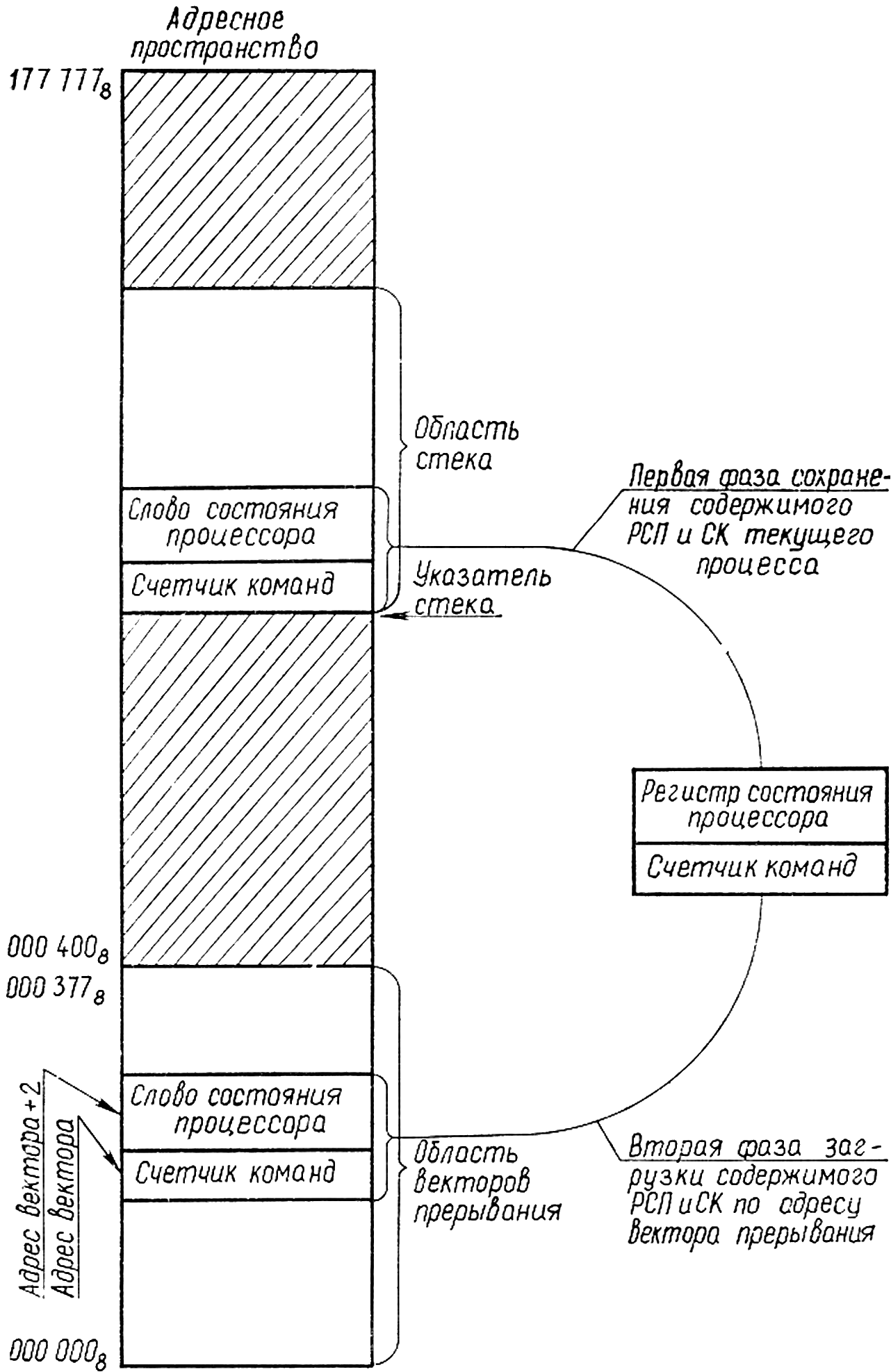

Прерывание - это временное прекращение выполнения текущей программы и переход к выполнению программы обслуживания устройства, вызвавшего прерывание. Каждое устройство, способное вызвать прерывание, должно иметь регистр состояния, содержащий разряд разрешения прерывания. Если устройству разрешается прерывание программы, то этот разряд должен быть программно установлен в единичное состояние. ОМП будет предоставлять прерывание и, следовательно, выполнять программу обслуживания устройства только в том случае, если седьмой разряд его РСП будет установлен в нулевое состояние. Каждое устройство, требующее прерывания, имеет программу обслуживания, вход в которую осуществляется автоматически с помощью вектора прерывания. Временная диаграмма приёма адреса вектора прерывания представлена на рис. 5.

Рис. 5. Временная диаграмма процедуры приёма адреса вектора прерывания

Последовательность операций при этом следующая:

- устройство, которому необходимо обслуживание, выставляет сигнал требования прерывания VIRQ;

- если прерывание разрешено, то процессор помещает в стек содержимое СК и РСП и последовательно устанавливает сигналы DIN и IAKO;

- устройство принимает сигнал IAKO и запрещает распространение этого сигнала к другим устройствам, помещает адрес вектора прерывания на выводы системной магистрали, вырабатывает сигнал RPLY и снимает сигнал VIRQ;

- процессор принимает адрес вектора прерывания и последовательно снимает сигналы DIN и IAKO;

- устройство завершает передачу вектора и снимает сигнал RPLY.

ОМП загружает новое содержимое СК и РСП из двух последовательных ячеек, первая из которых определяется адресом вектора прерывания, после чего переходит к выполнению программы обслуживания данного устройства. После завершения программы обслуживания ОМП возобновляет выполнение прерванной программы с помощью команды возврата из прерывания, по которой из стека выбираются два слова и записываются в СК и РСП.

Если имеется несколько устройств, способных запрашивать прерывание, то они соединяются по цепи предоставления прерывания (рис. 6). Прерывание текущего процесса и последующая его обработка производится после выполнения очередной команды. Прерывание по ошибке обращения к системной магистрали (обращение по адресу несуществующей ячейки памяти или регистра внешнего устройства) может прервать выполнение программы на любой фазе исполнения команды.

Рис. 6. Соединение нескольких устройств по цепи предоставления прерываний

Источниками прерываний, расположенными в соответствии с приоритетностью обработки (в случае одновременного появления нескольких запросов) являются:

- ошибка обращения к магистрали; резервный или запрещённый код в регистре команд;

- «Т-бит» в РСП;

- сигнал аварии сетевого питания ACLO;

- сигналы радиальных прерываний IRQ1, IRQ2, IRQ3;

- сигнал векторного прерывания VIRQ.

Установка седьмого разряда РСП в состояние «Лог.1» позволяет игнорировать сигналы прерывания VIRQ, IRQ2, IRQ3. Микропрограммная процедура прерывания ОМП разделяется на две фазы.

Первая фаза - сохранение значения вектора текущего процесса. При этом происходит запись в память по указателю стека (R6) с предварительным декрементом. Сначала записывается значение информации, содержащейся в РСП, затем - в СК.

Вторая фаза - загрузка значения вектора прерывания. ОМП формирует значение адреса вектора прерывания, по которому происходит загрузка СК и регистра слова состояния процессора (ССП) значениями двух ячеек памяти. ОМП анализирует состояние запросов па прерывание: если незамаскированных запросов нет, то происходит чтение первой команды нового процесса и её выполнение. Иначе снова происходит процедура прерывания (рис. 7).

Рис. 7. Условная схема процедуры прерывания

Однокристальный микропроцессор КМ1801ВМ2

Однокристальный микропроцессор КМ1801ВМ2 является дальнейшим развитием ОМП К1801ВМ1, обладает более высоким быстродействием, расширенной системой команд и рядом новых функциональных возможностей при применении в микро-ЭВМ. Имеет запасы по всем параметрам, что позволяет повысить экономические характеристики и, в конечном счёте, сделать микросхему доступной для самого широкого круга потребителей. Совместим по программному обеспечению и интерфейсу с ОМП К1801ВМ1. Основные параметры ОМП КМ1801ВМ2 приведены ниже.

|

Быстродействие выполнения регистровых команд типа «Сложение», операций/с |

до 1000 тыс. |

|

Быстродействие выполнения команд типа «Умножение», операций/с |

до 100 тыс. |

|

Максимальная тактовая частота, МГц |

10 |

|

Мощность потребления, Вт |

до 1,7 |

|

Конструкция |

металлокерамический 40-выводной корпус типа ДИП |

По сравнению с микросхемой К1801ВМ1 процессор КМ1801ВМ2 имеет расширенную систему команд (табл. 2).

|

№№ пп. |

Обозначение |

Код |

Наименование |

|---|---|---|---|

|

1 |

MUL |

070RSS |

Умножение |

|

2 |

DIV |

071RSS |

Деление |

|

3 |

ASH |

072RSS |

Сдвиг на N разрядов одного слова |

|

4 |

ASHC |

073RSS |

Сдвиг на N разрядов двойного слова |

|

5 |

FADD |

07500R |

Сложение с плавающей запятой |

|

6 |

FSUB |

07501R |

Вычитание с плавающей запятой |

|

7 |

FMUL |

07502R |

Умножение с плавающей запятой |

|

8 |

FDIV |

07503R |

Деление с плавающей запятой |

Команды расширенной арифметики (MUL, DIV, ASH, ASHC) реализованы на микропрограммном уровне в блоке микропрограммного управления ОМП. Выполнение команд с плавающей запятой (FADD, FSUB, FMUL, FDIV) обеспечивается на программном уровне с помощью системного ПЗУ К1801РЕ1.

Для повышения быстродействия выполнения последовательности команд в ОМП реализован конвейерный принцип приёма и выполнения команд, заключающийся в том, что к концу выполнения i-й команды (i+1)-я команда уже принята и процессор начинает приём (i+2)-й команды.

Условное графическое обозначение приведено на рис. 8. По сравнению с К1801ВМ1 микросхема КМ1801ВМ2 имеет ряд функциональных особенностей.

Рис. 8. Условное графическое обозначение микросхемы процессора КМ1801ВМ2

Сигнал выходной тактовой синхронизации CLC0 имеет частоту, равную половине частоты входной синхронизации CLC1. Он предназначен для организации систем, обладающих повышенной надёжностью, в которых несколько процессоров должны работать синхронно.

Микросхема КМ1801ВМ2 наряду с синхронной адресной частью обмена по системной магистрали имеет возможность асинхронной работы при передаче адреса. Это обеспечивается с помощью входного сигнала Адрес принят (AR). После выдачи адреса на системную магистраль ОМП ожидает появление сигнала AR. Низкий уровень входного сигнала AR свидетельствует о том, что пассивное устройство приняло адрес и ОМП может продолжать цикл обмена по системной магистрали.

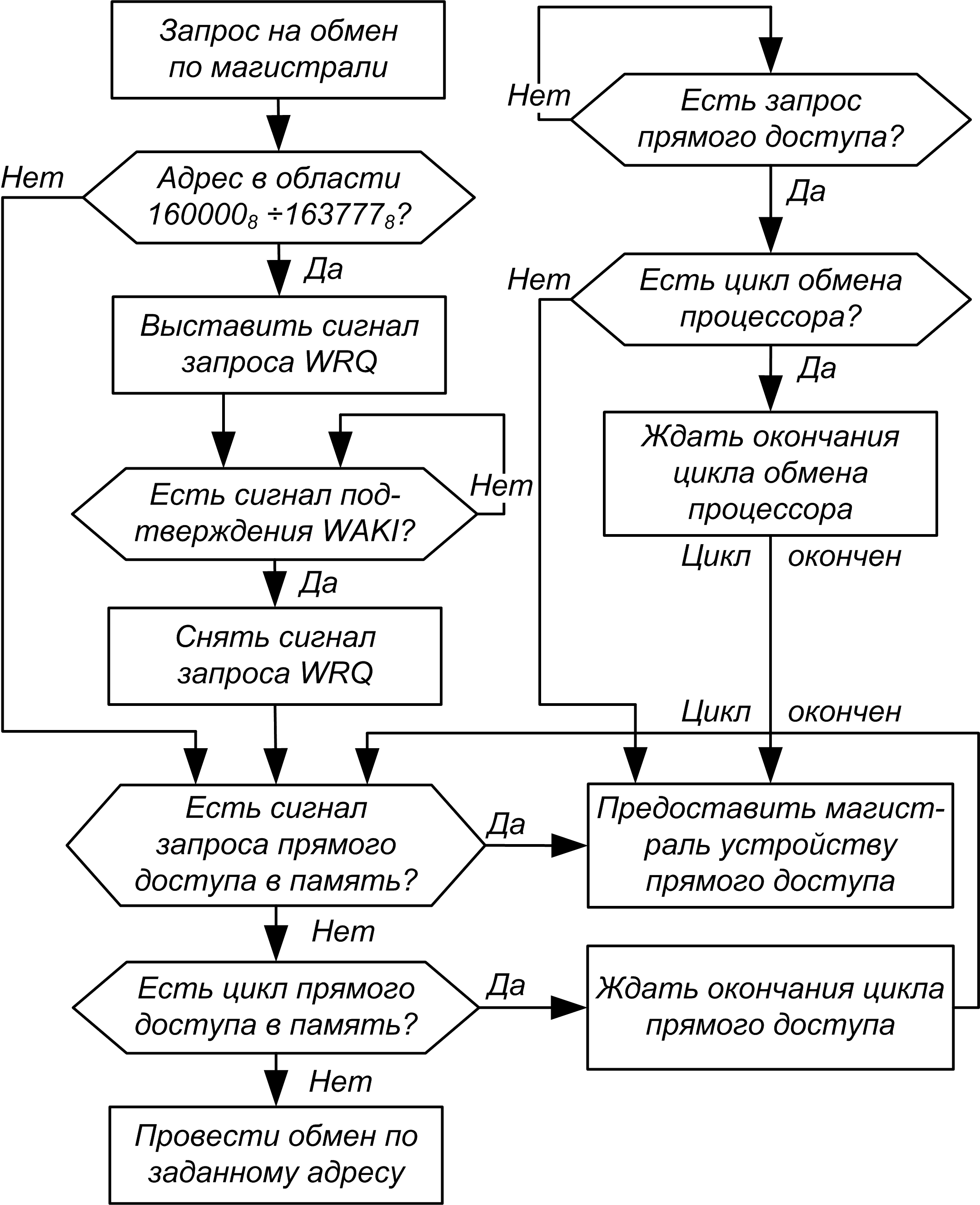

ОМП обладает встроенной логикой обращения в область адресного пространства от 160000(8) до 163777(8)включительно по специальной процедуре, представленной на рис. 9. Описанный механизм обращения в специальную область использует сигналы WRQ и WAKI и может применяться для организации обмена в многопроцессорных вычислительных системах.

Рис. 9. Процедура обмена процессора KM180IBM2 в специальной области

Сигнал SEL, устанавливаемый процессором в фазе чтения одновременно с сигналом DIN, определяет процедуру чтения внешнего регистра ввода-вывода. Обычно таким регистром является регистр начальных условий пуска процессора в составе ЭВМ. Если сигнал SEL ОМП устанавливает в фазе выдачи адреса, то это означает, что обмен идёт с системной памятью, в качестве которой используется микросхема К1801РЕ1. Системная память помимо специальных программ (начального пуска, резидентного тестового обеспечения, пультового терминала) позволяет расширять систему команд с помощью программной реализации дополнительных команд.

Системная память при работе с ОМП является «скрытой», т.е. её адреса в программном режиме не занимают адресного пространства ОЗУ. Тем самым она дополняет оперативную память. Системная память программно доступна с помощью специальных команд ОМП. Сигнал HALT аналогичен сигналу IRQ1, сигнал EVNT (прерывание от таймера) аналогичен сигналу IRQ2 в ОМП К1801ВМ1.

Развитие однокристальных микропроцессоров комплекта

Применение перспективной технологии изготовления БИС, автоматизированных систем проектирования и контроля позволяет определить следующие основные направления развития однокристальных ОМП комплекта БИС серий К1801/К1809, реализуемых в настоящее время:

- увеличение быстродействия выполнения команд в 2,3 раза по сравнению с ОМП КМ1801ВМ2, расширение системы команд и адресного пространства до 4 Мбайт;

- совершенствование структуры ОМП, обеспечивающее диспетчеризацию памяти, возможность организации многопроцессорных систем, обнаружение и коррекцию ошибок информации, введение периферийного арифметического процессора;

- использование различных конструктивных исполнений микросхем: металлокерамические планарные корпуса, пластмассовые и металлокерамические корпуса типа ДИП;

- переход на перспективную КМОП-технологию изготовления.

Высокие технические характеристики, совместимость по интерфейсу, системе команд и программному обеспечению с рядом микро-ЭВМ «Электроника 60», программная совместимость с рядом СМ ЭВМ (СМ-3/СМ-4) определяют широкую перспективу применения однокристальных процессоров серии К1801.

Статья поступила 16 октября 1984 г.

(прим. gid: списка литературы нет, а ссылки на него в тексте есть.)